# EDITED BY Gernot Hueber Ali M. Niknejad

# Millimeter-Wave Circuits for 5G and Radar

THE CAMBRIDGE RF AND MICROWAVE ENGINEERING SERIES

## Millimeter-Wave Circuits for 5G and Radar

Discover the concepts, architectures, components, tools, and techniques needed to design millimeter-wave circuits for current and emerging wireless system applications. Focusing on applications in 5G, connectivity, radar, and more, leading experts in radio-frequency integrated circuit (RFIC) design provide a comprehensive treatment of cutting-edge physical-layer technologies for RF transceivers – specifically RF, analog, mixed-signal, and digital circuits and architectures. The full design chain is covered, from system design requirements to building blocks, transceivers, and process technology. Gain insight into the key novelties of 5G through authoritative chapters on massive MIMO and phased arrays, and learn about the very latest technology developments, such as FinFET logic process technology for RF and millimeter-wave applications. This is an excellent reference and essential reading for high-frequency circuit designers in both academia and industry.

**Gernot Hueber** is Chief Scientist RF at Silicon Austria Labs leading the RF Research Unit. Previously, he held various positions in industry and academia in the field of wireless communications. He has published extensively on RFICs, and has over 60 patents in the field.

**Ali M. Niknejad** is a Professor in the Department of Electrical Engineering and Computer Sciences at the University of California, Berkeley, and Faculty Director of the Berkeley Wireless Research Center. He is the author of *Electromagnetics for High-Speed Analog and Digital Communication Circuits* (Cambridge University Press, 2007) and a fellow of the Institute of Electrical and Electronics Engineers (IEEE).

## The Cambridge RF and Microwave Engineering Series

**Series Editor**

Steve C. Cripps, Distinguished Research Professor, Cardiff University

#### **Editorial Advisory Board**

James F. Buckwalter, UCSB Jenshan Lin, University of Florida John Wood, Maxim Integrated Products

Peter Aaen, Jaime Plá and John Wood, Modeling and Characterization of RF and Microwave Power FETs

Dominique Schreurs, Máirtín O'Droma, Anthony A. Goacher and Michael Gadringer (Eds), *RF Amplifier Behavioral Modeling*

Fan Yang and Yahya Rahmat-Samii, *Electromagnetic Band Gap Structures in Antenna Engineer*ing

Enrico Rubiola, Phase Noise and Frequency Stability in Oscillators

Earl McCune, Practical Digital Wireless Signals

Stepan Lucyszyn. Advanced RF MEMS

Patrick Roblin, Nonlinear RF Circuits and the Large-Signal Network Analyzer

Matthias Rudolph, Christian Fager and David E. Root (Eds), Nonlinear Transistor Model Parameter Extraction Techniques

John L. B. Walker (Ed.), Handbook of RF and Microwave Solid-State Power Amplifiers

Anh-Vu H. Pham, Morgan J. Chen and Kunia Aihara, *LCP for Microwave Packages and Modules* Sorin Voinigescu, *High-Frequency Integrated Circuits*

Richard Collier, Transmission Lines

Valeria Teppati, Andrea Ferrero and Mohamed Sayed (Eds), Modern RF and Microwave Measurement Techniques

Nuno Borges Carvalho and Dominique Schreurs, Microwave and Wireless Measurement Techniques

David E. Root, Jason Horn, Jan Verspecht and Mihai Marcu, X-Parameters

Earl McCune, Dynamic Power Supply Transmitters

Hossein Hashemi and Sanjay Raman (Eds), *Silicon mm-Wave Power Amplifiers and Transmitters* T. Mitch Wallis and Pavel Kabos, *Measurement Techniques for Radio Frequency Nanoelectronics* Giovanni Ghione and Marco Pirola, *Microwave Electronics*

Isar Mostafanezhad, Olga Boric-Lubecke and Jenshan Lin (Eds), Medical and Biological Microwave Sensors

Richard Carter, Microwave and RF Vacuum Electronic Power Sources

José Carlos Pedro, David Root, Jianjun Xu and Luis Cotimos Nunes, Nonlinear Circuit Simulation and Modeling

Gernot Hueber and Ali M. Niknejad, Millimeter-Wave Circuits for 5G and Radar

# Millimeter-Wave Circuits for 5G and Radar

Edited by

GERNOT HUEBER

Silicon Austria Labs, Austria

ALI M. NIKNEJAD University of California, Berkeley

## CAMBRIDGE UNIVERSITY PRESS

University Printing House, Cambridge CB2 8BS, United Kingdom

One Liberty Plaza, 20th Floor, New York, NY 10006, USA

477 Williamstown Road, Port Melbourne, VIC 3207, Australia

314-321, 3rd Floor, Plot 3, Splendor Forum, Jasola District Centre, New Delhi - 110025, India

79 Anson Road, #06-04/06, Singapore 079906

Cambridge University Press is part of the University of Cambridge.

It furthers the University's mission by disseminating knowledge in the pursuit of education, learning, and research at the highest international levels of excellence.

www.cambridge.org Information on this title: www.cambridge.org/9781108492782 DOI: 10.1017/9781108686396

© Cambridge University Press 2019

This publication is in copyright. Subject to statutory exception and to the provisions of relevant collective licensing agreements, no reproduction of any part may take place without the written permission of Cambridge University Press.

First published 2019

Printed in the United Kingdom by TJ International Ltd, Padstow Cornwall

A catalogue record for this publication is available from the British Library.

Library of Congress Cataloging-in-Publication Data

Names: Hueber, Gernot, 1972- | Niknejad, Ali M., 1972-

Title: Millimeter-wave circuits for 5G and radar / edited by Gernot Hueber, Silicon Austria Labs, Austria, Ali M. Niknejad, University of California, Berkeley.

Description: Cambridge, United Kingdom ; New York, NY, USA : Cambridge University Press, 2019. | Series: The Cambridge RF and microwave engineering series | Includes bibliographical references and indexes.

Identifiers: LCCN 2018060438 | ISBN 9781108492782 (hardback)

- Subjects: LCSH: Millimeter wave devices. | Wireless communication systems-Equipment and supplies. | Radar circuits.

- Classification: LCC TK7876.5 .M45 2019 | DDC 621.3848-dc23 LC record available at https://lccn.loc.gov/2018060438

ISBN 978-1-108-49278-2 Hardback

Cambridge University Press has no responsibility for the persistence or accuracy of URLs for external or third-party internet websites referred to in this publication and does not guarantee that any content on such websites is, or will remain, accurate or appropriate.

"The 5G cellular standard has been under development for a number of years and is projected to support speeds far greater than those of earlier generations. This ambitious goal relies on innovations at all levels of abstraction, and is well served by the publication of *Millimeter-Wave Circuits for 5G and Radar*. Written by nearly 30 experts in the field, this book provides a great overview of the state of the art and will benefit those who wish to advance their knowledge of millimeter-wave circuits."

## Behzad Razavi, UCLA

"A book of landmark importance for practitioners of 5G radio frequency (RF) system and RF circuit design covering millimeter-wave and frequency division duplex (FDD) transceivers. It covers the essential topics of transceiver system design, beam forming, and circuit design for advanced 5G and radar systems."

Kamal Sahota, Qualcomm

"This book is an excellent read with topics ranging from architecture to layouts, and the concepts are illustrated by test results from manufactured circuits in advance technology nodes. Leading industry and academic researchers give a comprehensive overview of system aspects as well as in-depth state-of-the-art circuit design solutions. The scope is also very timely, as integration of advanced radio and radar transceivers is the key enabling technology for 5G communication and automotive application hardware."

Sven Mattisson, Ericsson

"This book is on the 5G system and radar, which are both part of our future indeed. A wide range of experts have been brought together to discuss the design of high-frequency circuitry for 5G and radar. Both the system level and the transistor level are addressed in great detail. It includes 5G system considerations and transceivers, digital phase-locked loops (PLLs), voltage-controlled oscillators (VCOs), power amplifiers, etc. Actually, in systems of such complexity, few circuits of importance can be missing. Linearity and noise considerations are omnipresent as well. The last chapter provides the trade-off between planar complementary metal-oxide semiconductors (CMOS) and Fin Field-effect transistors (FinFETs). This is a choice that each designer faces sooner or later. As a result, this book is a must for whoever wants to play a design role in the coming 5G or radar systems."

Willy Sansen, KU Leuven

## Contents

1

2

3

| Con   | tributors                                                                      | <i>page</i> xiv |

|-------|--------------------------------------------------------------------------------|-----------------|

| Fore  | eword                                                                          | xvii            |

| Intro | oduction                                                                       | 1               |

| Gerne | ot Hueber and Ali M. Niknejad                                                  |                 |

| 1.1   | 5G                                                                             | 1               |

|       | 1.1.1 What Is 5G?                                                              | 1               |

|       | 1.1.2 A Brief History of the Gs                                                | 2               |

|       | 1.1.3 Do We Need 5G?                                                           | 4               |

| 1.2   | Radar                                                                          | 10              |

| 1.3   | A Circuit Designer's Perspective                                               | 13              |

|       | Transceivers from Requirements to System Models and Analysis o Pärssinen       | 18              |

| 2.1   | RF Requirements Inspired by 5G System Targets                                  | 18              |

| 2.1   | Radio Spectrum and Standardization                                             | 20              |

|       | System Scalability                                                             | 20              |

|       | Communications System Model for RF System Analysis                             | 22              |

| 2.5   |                                                                                | 29              |

| 2.5   | 2.5.1 Transmitter                                                              | 29              |

|       | 2.5.2 Receiver                                                                 | 31              |

|       | 2.5.3 Antenna Array                                                            | 33              |

|       | 2.5.4 Transceiver Architectures for RF and Hybrid Beamforming                  | 36              |

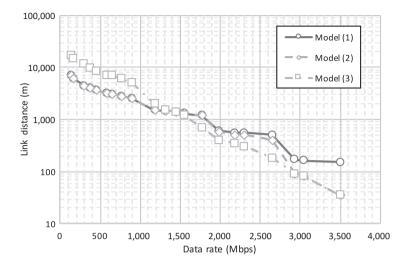

| 2.6   | Radio Propagation and Link Budget                                              | 38              |

| 2.7   |                                                                                | 43              |

|       | Conclusion                                                                     | 51              |

|       | MIMO and Massive MIMO for 5G Radios                                            | 55              |

| Antor | nio Puglielli, Greg LaCaille, Elad Alon, Borivoje Nikolić, and Ali M. Niknejad |                 |

| 3.1   | Spatial Processing: Untapped Potential                                         | 55              |

| 3.2   | MIMO Technology Overview                                                       | 56              |

vii

|            | 3.2.1    | Spatial Multiplexing with Antenna Arrays                                   | 58     |

|------------|----------|----------------------------------------------------------------------------|--------|

|            | 3.2.2    | MIMO: Exploiting Multipath Propagation                                     | 60     |

|            | 3.2.3    | Channel Rank                                                               | 62     |

|            | 3.2.4    | Multiuser MIMO (MU-MIMO)                                                   | 63     |

| 3.3        | Conve    | entional MIMO Processing                                                   | 64     |

|            | 3.3.1    | Channel Estimation                                                         | 64     |

|            | 3.3.2    | Linear Beamforming                                                         | 65     |

|            | 3.3.3    | ML and Near-ML Receivers                                                   | 66     |

|            | 3.3.4    | Successive Interference Cancellation                                       | 67     |

|            | 3.3.5    | MU Downlink: Dirty Paper Coding                                            | 68     |

|            | 3.3.6    | Massive MIMO: High-Order MU-MIMO                                           | 68     |

| 3.4        | System   | n Architecture for Large Arrays                                            | 69     |

|            | 3.4.1    | State of the Art                                                           | 7(     |

|            | 3.4.2    | A Scalable Beamforming-Aware Array Architecture                            | 71     |

| 3.5        | Impair   | rments in Large Arrays                                                     | 76     |

|            | 3.5.1    | Synchronization                                                            | 76     |

|            | 3.5.2    | Reciprocity and Channel Estimation                                         | 77     |

|            | 3.5.3    | Transmit Linearity                                                         | 78     |

| 3.6        | Conclu   | usion                                                                      | 78     |

| 4.1<br>4.2 |          | iew of Full-Duplex<br>neter-Wave Full-Duplex Applications                  | 8<br>8 |

| 4.2        |          | Millimeter-Wave Backhaul                                                   | 80     |

|            |          | Milimeter-Wave FD Relaying                                                 | 80     |

|            |          | Millimeter-Wave FD Kelaying<br>Millimeter-Wave Vehicular Radar             | 8      |

|            |          | 5G Small-Cell Base Stations                                                | 88     |

|            |          | Virtual Reality (VR)/Augmented Reality (AR) Headsets                       | 88     |

| 4.3        |          | Ouplex Challenge and System Considerations                                 | 88     |

| 4.4        |          | nterference Suppression Techniques                                         | 92     |

|            |          | Antenna Suppression                                                        | 92     |

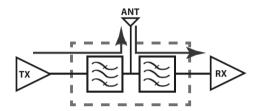

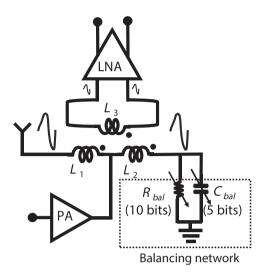

|            |          | Shared Antenna Interface                                                   | 94     |

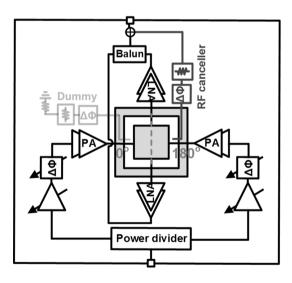

|            |          | Integrated Low-RF FD Radios                                                | 98     |

|            | 4.4.4    | Integrated Millimeter-Wave FD Radios                                       | 103    |

| 4.5        | Conclu   | 6                                                                          | 100    |

|            |          |                                                                            |        |

|            |          | grated Architectures for Frequency Division<br>munication                  | 112    |

| -          |          |                                                                            | 11.    |

| Lucas      | A. Calde | rin, Sameet Ramakrishnan, Elad Alon, Borivoje Nikolić, and Ali M. Niknejad |        |

| 5.1        | Introd   | uction                                                                     | 112    |

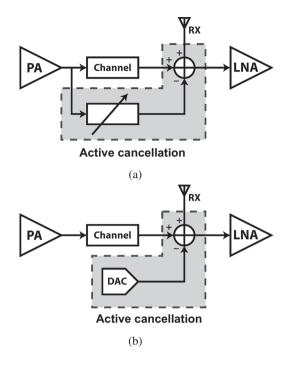

| 5.2        | Annro    | aches to Self-Interference Cancellation                                    | 113    |

4

5

|        | 5.2.1 Hybrids                                                   | 113 |

|--------|-----------------------------------------------------------------|-----|

|        | 5.2.2 Active Cancellation                                       | 114 |

| 5.3    | System Concept and Architecture                                 | 115 |

|        | 5.3.1 Conceptual Overview                                       | 115 |

| 5.4    | System Implementation Considerations                            | 117 |

|        | 5.4.1 DAC Power Consumption                                     | 117 |

|        | 5.4.2 System Thermal Noise                                      | 118 |

| 5.5    | System Degradation                                              | 123 |

| 5.6    | Transmitter                                                     | 124 |

| 5.7    | Cancellation DAC Design                                         | 126 |

|        | 5.7.1 DAC Linearity                                             | 126 |

|        | 5.7.2 DAC Thermal Noise Cancellation                            | 127 |

| 5.8    | Quantization Noise Measurements                                 | 130 |

|        | 5.8.1 Channel Memory                                            | 130 |

|        | 5.8.2 PA Dynamic Nonlinearity                                   | 132 |

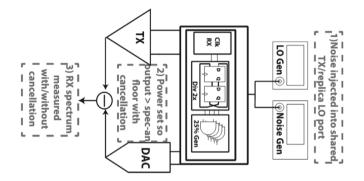

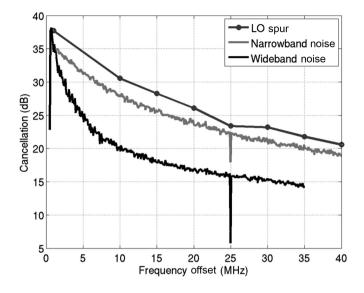

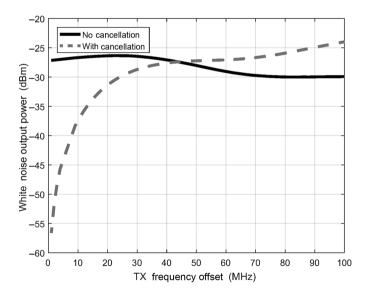

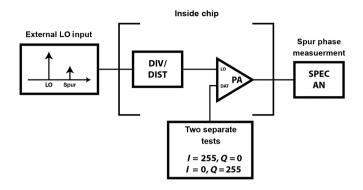

| 5.9    | Measurement Results                                             | 135 |

| 5.10   | Conclusion                                                      | 143 |

| Scala  | able RF and Millimeter-Wave Multibeam Approaches                | 146 |

|        | Vatarajan                                                       |     |

| 6.1    | Large-Scale Phased and MIMO Arrays                              | 146 |

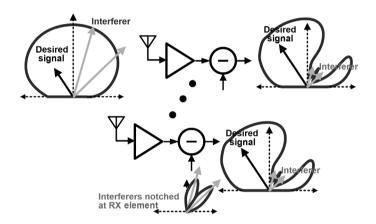

| 6.2    | Reconfigurable Spatial Filtering                                | 147 |

|        | 6.2.1 MIMO Spatial Filtering at RF                              | 148 |

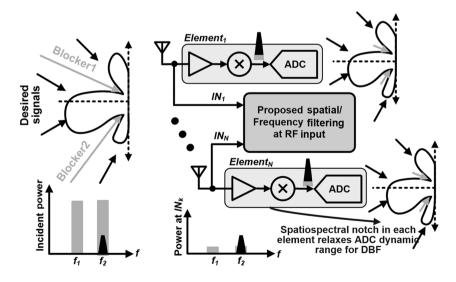

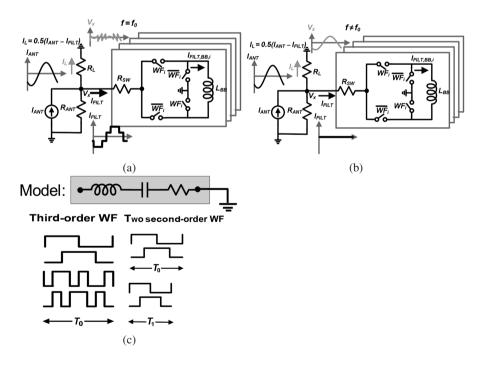

| 6.3    | N-Path Spatiospectral Filtering                                 | 149 |

| 6.4    | Scalable mm-Wave Packaging                                      | 152 |

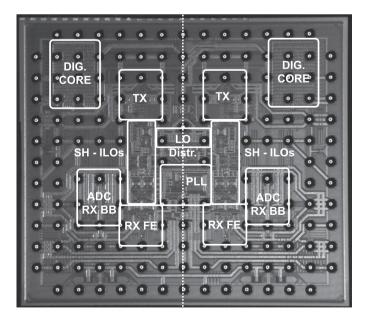

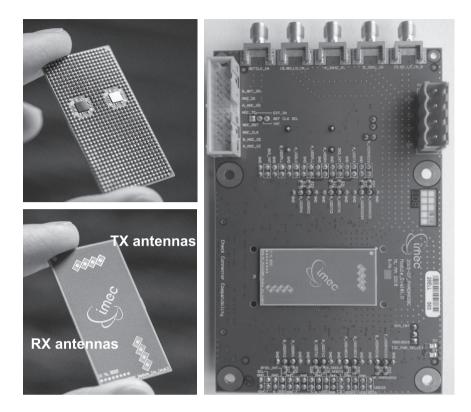

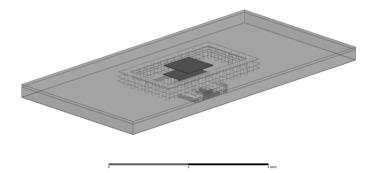

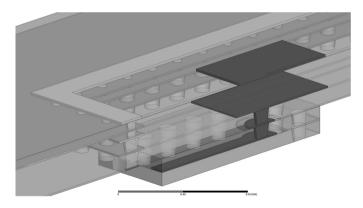

| Millin | meter-Wave Radar SoC Integration in CMOS                        | 162 |

| Piet W | Jambacq, Davide Guermandi, André Bourdoux, and Jan Craninckx    |     |

| 7.1    | Introduction                                                    | 162 |

| 7.2    | Frequency-Modulated Continuous-Wave Radar                       | 164 |

| 7.3    | Phase-Modulated Continuous-Wave Radar                           | 166 |

| 7.4    | Comparison between FMCW and PMCW                                | 168 |

|        | 7.4.1 Sensitivity to Phase Noise and Flicker Noise              | 168 |

|        | 7.4.2 TX Orthogonality for MIMO Radar                           | 168 |

|        | 7.4.3 Interference Robustness                                   | 168 |

|        | 7.4.4 IF Bandwidth and ADC                                      | 168 |

|        | 7.4.5 TX-to-RX Spillover                                        | 169 |

|        | 7.4.6 Waveform Generation and Linearity                         | 169 |

|        | 7.4.7 Other Aspects                                             | 169 |

| 7.5    | Link Budget for a PMCW Radar                                    | 169 |

|        | 7.5.1 Link Budget for Single-Antenna TX and RX and MIMO Systems | 170 |

|        | 7.5.2 LO Phase Noise                                            | 172 |

6

7

іх

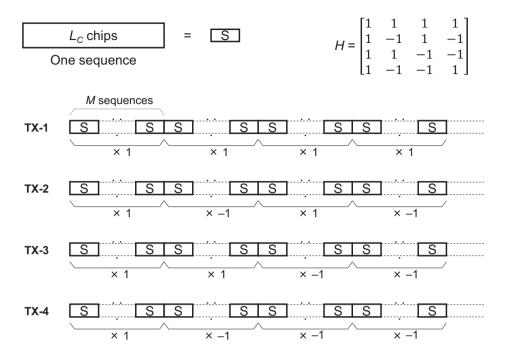

| 7.6   | MIMO      | D Techniques for PMCW Radars                                   | 172 |

|-------|-----------|----------------------------------------------------------------|-----|

|       | 7.6.1     | TX Orthogonality by Sequence Engineering: Different            |     |

|       |           | TX Use Different Sequences                                     | 173 |

|       | 7.6.2     | TX Orthogonality with Outer Code: All TX Use the Same Sequence | 173 |

|       |           | Comparison of the Two Approaches and Implementation            | 173 |

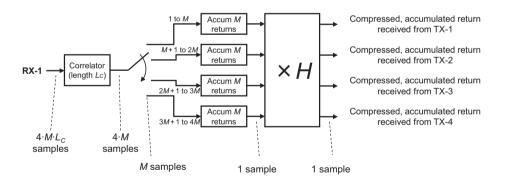

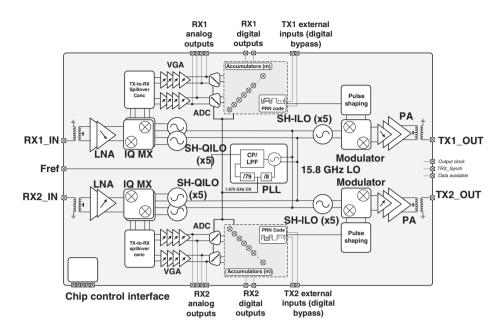

| 7.7   |           | g and Millimeter-Wave Circuits                                 | 174 |

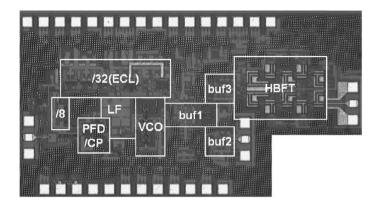

|       | 7.7.1     | Frequency Generation                                           | 175 |

| 7.8   | Exper     | imental Results                                                | 18  |

|       | 7.8.1     | Module and Antenna Design                                      | 181 |

|       |           | Circuit-Level Measurements                                     | 182 |

|       | 7.8.3     | Radar System Measurements                                      | 186 |

|       | 7.8.4     | Conclusions and State-of-the-Art Comparison                    | 189 |

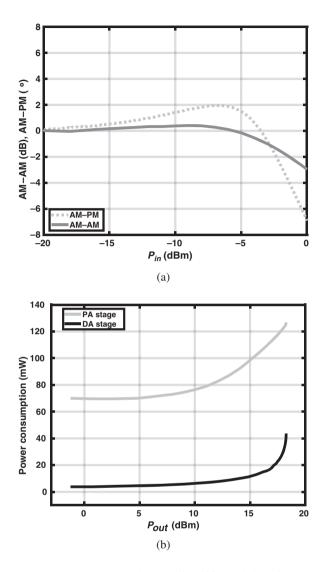

| СМО   | S Trans   | ceiver Design for Ultra-High-Speed Millimeter-Wave             |     |

| Wire  | less Co   | mmunications                                                   | 193 |

| Kenic | hi Okada  | and Rui Wu                                                     |     |

| 8.1   | Introd    | uction                                                         | 193 |

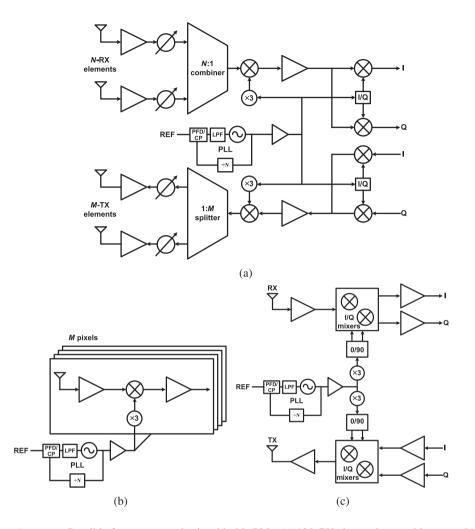

| 8.2   | 60 GH     | Iz CMOS Transceiver Architecture                               | 194 |

|       | 8.2.1     | Challenges and Design Considerations                           | 194 |

|       | 8.2.2     | Direct-Conversion Transceiver Architecture                     | 20  |

| 8.3   | Circui    | t Implementation of Key Building Blocks                        | 202 |

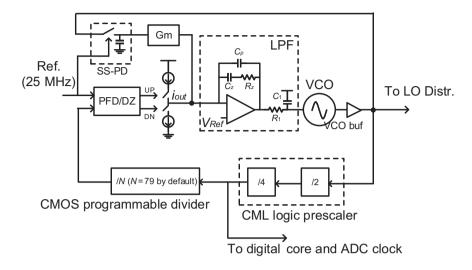

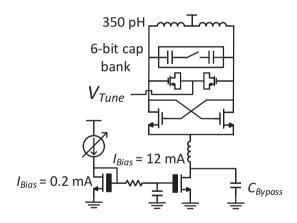

|       | 8.3.1     | Local Synthesizer                                              | 202 |

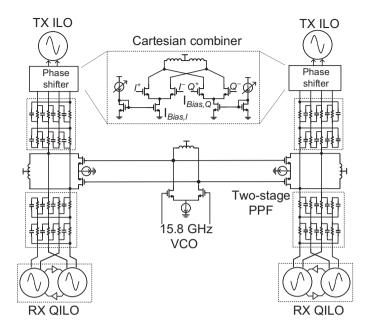

|       | 8.3.2     | Transmitter                                                    | 205 |

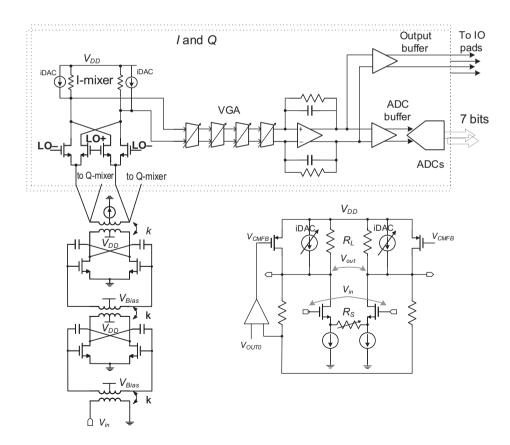

|       | 8.3.3     | Receiver                                                       | 21  |

|       | 8.3.4     | Calibration Techniques                                         | 21′ |

| 8.4   | Measu     | rement Results of Transceiver Chips                            | 224 |

| 8.5   | Concl     | usion                                                          | 230 |

| Phas  | sed Arra  | ays for 5G Millimeter-Wave Communications                      | 243 |

| Bodhi | isatwa Sa | dhu and Leonard Rexberg                                        |     |

| 9.1   |           | ole of mm-Wave in 5G Communications                            | 243 |

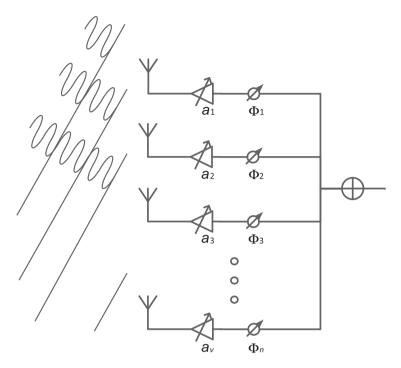

| 9.2   | Introd    | uction to Beamforming                                          | 244 |

|       | 9.2.1     | Beamforming as a Fourier Transform                             | 244 |

|       | 9.2.2     | Beam Shaping and Beam Steering                                 | 249 |

|       | 9.2.3     | 2D Antenna Array                                               | 250 |

| 9.3   | Desire    | ed Features of Millimeter-Wave Phased Arrays                   | 252 |

|       | 9.3.1     | Accurate Beam Control                                          | 252 |

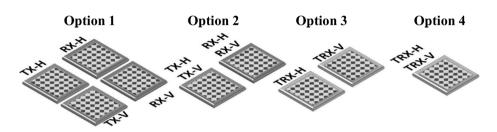

|       | 9.3.2     | Architecture Scalability                                       | 253 |

|       | 9.3.3     | Dual-Polarized Operation                                       | 254 |

|       | 9.3.4     | Small Solution Footprint                                       | 255 |

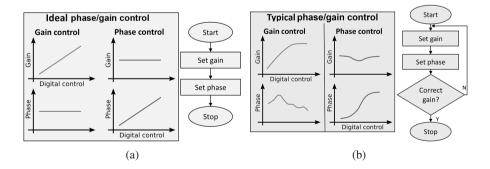

|       | 9.3.5     | Orthogonal Phase and Gain Control                              | 257 |

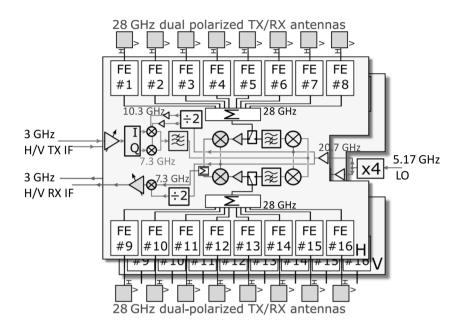

| 9.4   | Exem      | plary Si-Based Millimeter-Wave Phased Array                    | 258 |

8

9

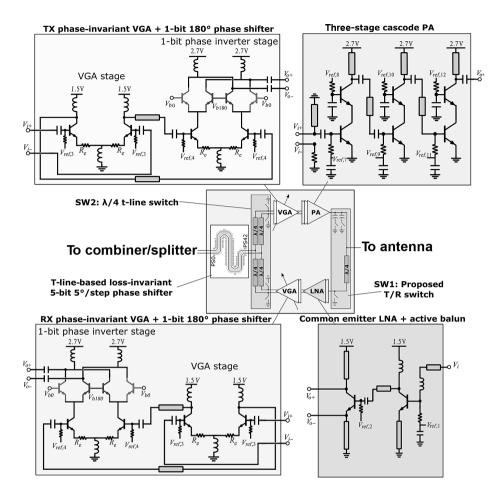

|       | 9.4.1 Circuit Details                                             | 258 |

|-------|-------------------------------------------------------------------|-----|

|       | 9.4.2 Measurement Results                                         | 263 |

| 9.5   | Conclusion                                                        | 270 |

| Milli | neter-Wave Frequency Synthesis Based on Frequency Multiplications | 273 |

|       | Heydari                                                           |     |

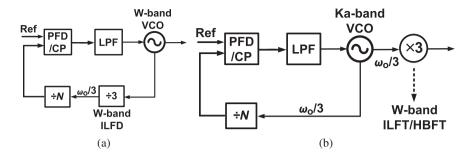

| 10.1  | Introduction and Motivation                                       | 273 |

| 10.2  | Design of a Silicon-Based Ka-Band PLL                             | 279 |

|       | Design of a W-Band ILFT                                           | 280 |

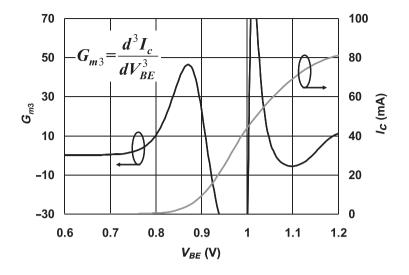

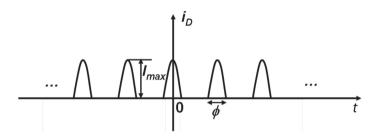

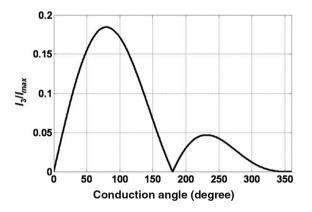

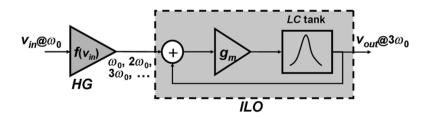

|       | 10.3.1 Harmonic Generation of HBT                                 | 280 |

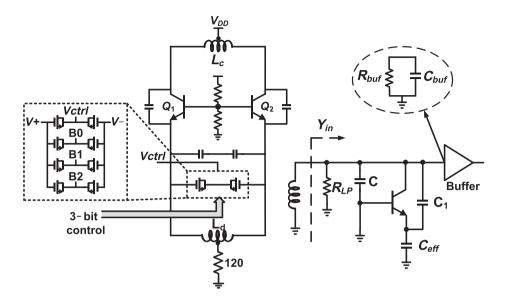

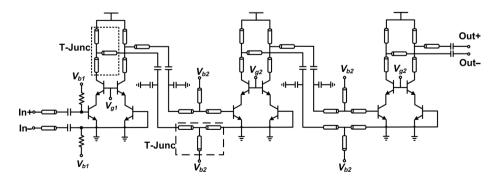

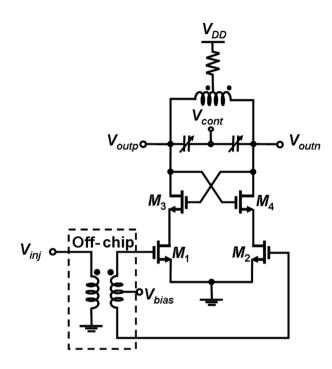

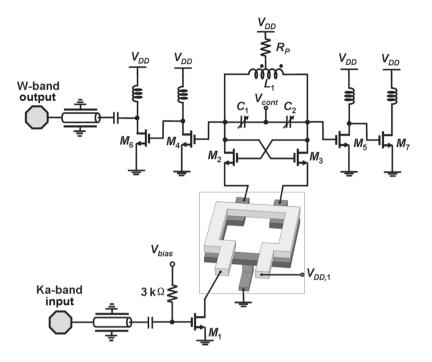

|       | 10.3.2 Circuit Design of the mm-Wave ILFT                         | 281 |

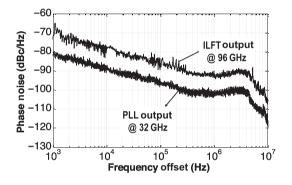

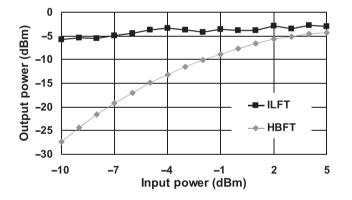

|       | 10.3.3 Measurement Results                                        | 286 |

| 10.4  | Design of a W-Band Silicon-Based HBFT                             | 287 |

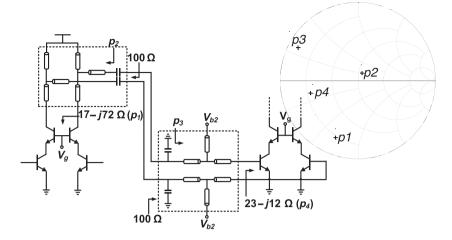

|       | 10.4.1 Circuit Design of the mm-Wave HBFT                         | 287 |

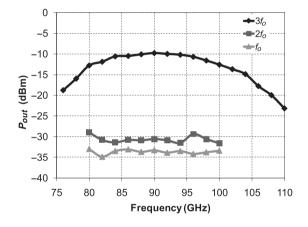

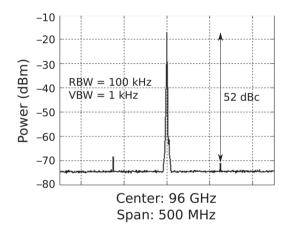

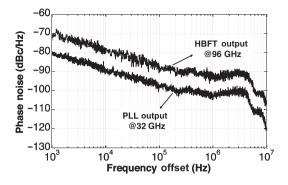

|       | 10.4.2 Measurement Results                                        | 289 |

| 10.5  | Design of a Transformer-Based CMOS ILFT                           | 291 |

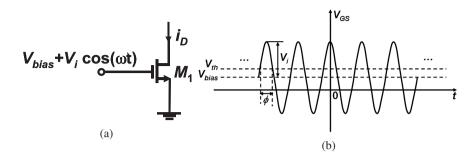

|       | 10.5.1 Harmonic Generation of an MOS Transistor                   | 291 |

|       | 10.5.2 Millimeter-Wave T-ILFT Structure                           | 293 |

|       | 10.5.3 Measurement Results                                        | 296 |

| 10.6  | Comparisons and Discussions                                       | 300 |

| 10.7  | Conclusions                                                       | 302 |

| Digit | ally Intensive PLL and Clock Generation                           | 305 |

| Wang  | Wu and R. Bogdan Staszewski                                       |     |

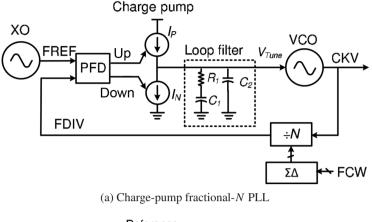

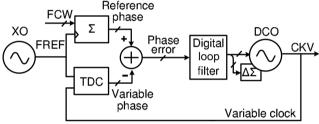

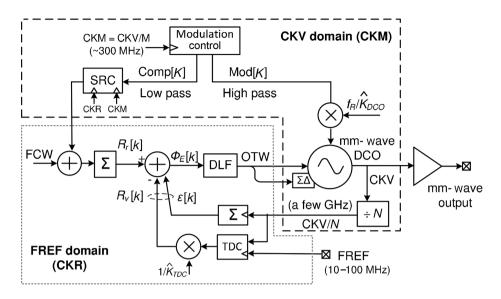

| 11.1  | Introduction to Digitally Intensive PLL                           | 305 |

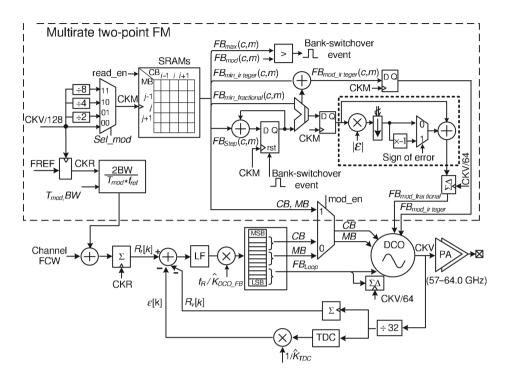

| 11.2  | Multirate DPLL-Based Frequency Modulator Architecture             | 309 |

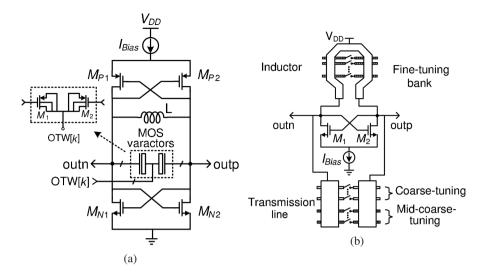

| 11.3  | High-Resolution mm-Wave DCOs                                      | 312 |

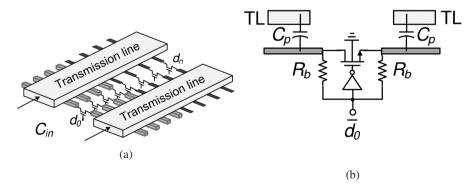

|       | 11.3.1 Distributed Switched Metal Capacitor Bank for              |     |

|       | mm-Wave DCOs                                                      | 312 |

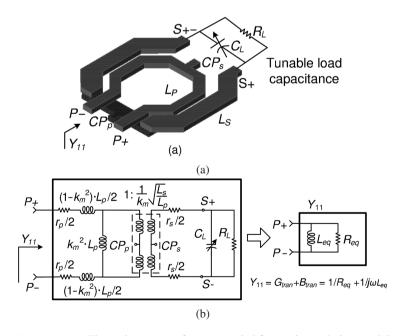

|       | 11.3.2 Transformer-Coupled Fine-Tuning Bank                       | 315 |

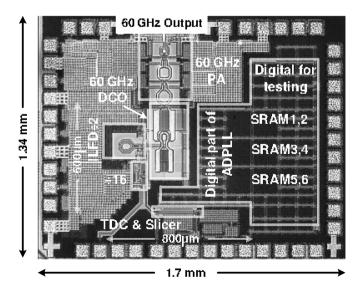

|       | 11.3.3 A 60 GHz DCO Design Example                                | 317 |

| 11.4  | Time-to-Digital Converter                                         | 319 |

| 11.5  | Digital Calibration Techniques for High RF Performance            | 324 |

|       | 11.5.1 DCO Gain Calibration and Linearization                     | 324 |

11.5.2 Mismatch Calibration of the Fine-Tuning Bank

11.6 Built-In Self-Test and Built-In Self-Characterization for DPLL

11.6.1 Critical Signals in DPLL for BIST and BISC

11.6.2 Snapshotting Internal Signals for Debugging

11.7 Another Approach: DTC-Assisted DPLL Architecture

11.5.3 Synchronization in a Multirate System

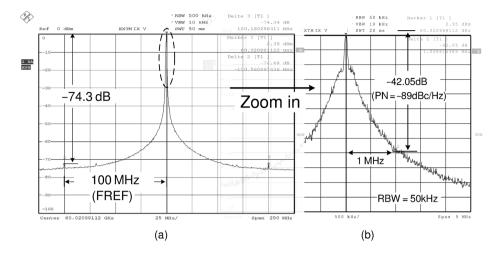

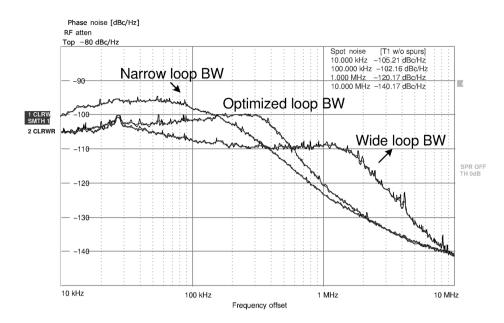

11.5.4 Experimental Results

11.6.3 DCO Tuning Step Analyzer

10

11

xi

326 327

328

331

333

336

337

337

| 12 | Practical VCO Design<br>Mohyee Mikhemar                                                   | 347        |

|----|-------------------------------------------------------------------------------------------|------------|

|    | 12.1 LO Design                                                                            | 347        |

|    | 12.1.1 LO Architectures                                                                   | 348        |

|    | 12.1.2 Impact of LO Architecture on VCO Requirements                                      | 349        |

|    | 12.2 Fundamentals of VCO Design                                                           | 350        |

|    | 12.2.1 Improving Noise Factor by Avoiding Triode Operation                                | 354        |

|    | 12.3 VCO Frequency Scaling                                                                | 356        |

|    | 12.4 Design Procedure                                                                     | 358        |

|    | 12.5 Practical Considerations in VCO Design                                               | 359        |

|    | 12.5.1 Tail Tuning and Bypass Capacitance                                                 | 360        |

|    | 12.5.2 Kickback from the First VCO Buffer                                                 | 362        |

|    | 12.5.3 Resilience to Pulling                                                              | 364        |

|    | 12.5.4 AM/PM Conversion in Small Tuning-Range VCO Designs                                 | 364        |

|    | 12.5.5 Bias Circuit Design for VCO                                                        | 365        |

|    | 12.6 Conclusion                                                                           | 366        |

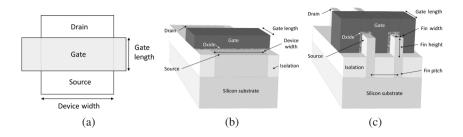

| 13 | CMOS Power Amplifier Design for 5G Mobile Applications<br>Yang Zhang and Patrick Reynaert | 369        |

|    | 13.1 Introduction                                                                         | 369        |

|    | 13.2 5G RF Front-End Requirement                                                          | 369        |

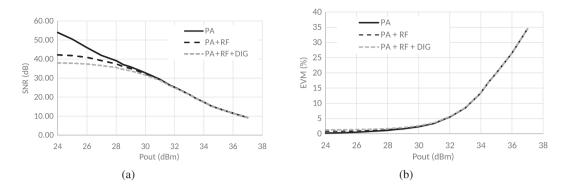

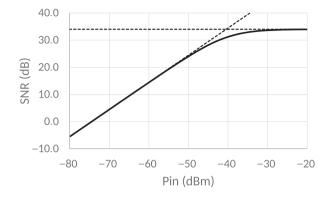

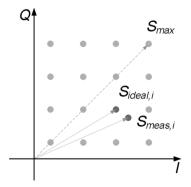

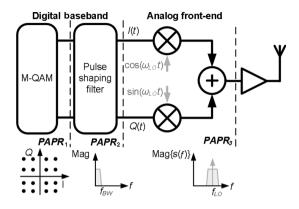

|    | 13.2.1 Quantify the Signal Quality                                                        | 370        |

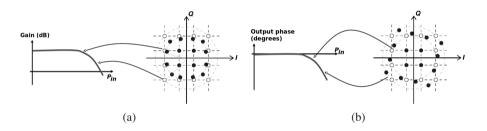

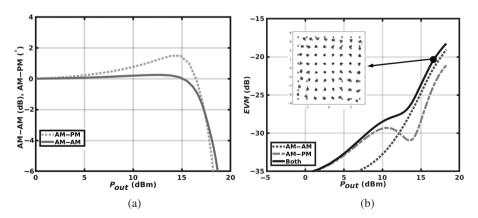

|    | 13.2.2 Signal Influenced by PA Nonlinearities                                             | 373        |

|    | 13.3 Power Amplifier Basics                                                               | 374        |

|    | 13.3.1 Transistor Optimization for PAs                                                    | 375        |

|    | 13.3.2 Passive Device in CMOS                                                             | 375        |

|    | 13.4 Impedance Transformation and Power Combining                                         | 379        |

|    | 13.4.1 PA Nonlinearity                                                                    | 381        |

|    | 13.4.2 Linearity Enhancement Technology                                                   | 382        |

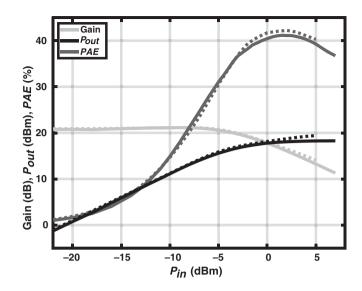

|    | 13.5 Design Example of a 40 nm CMOS PA                                                    | 384        |

|    | 13.5.1 Power Transistor with Source Degeneration Inductor                                 | 384        |

|    | 13.5.2 Design                                                                             | 385        |

|    | 13.5.3 Measurement Results                                                                | 389        |

|    | 13.6 Conclusion                                                                           | 395        |

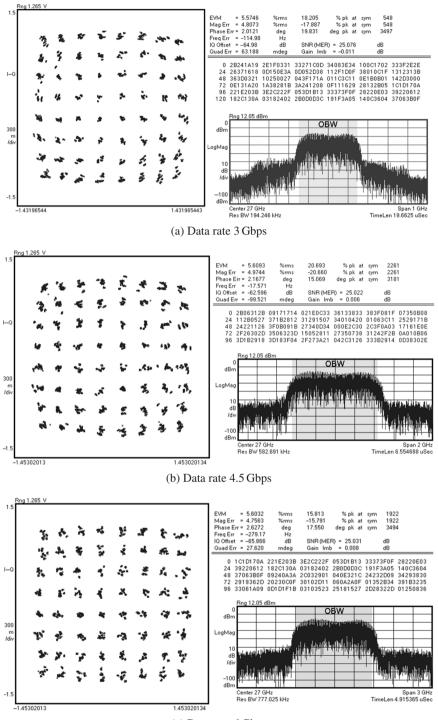

| 14 | FinFET Process Technology for RF and Millimeter-Wave Applications                         | 400        |

|    | Hyung-Jin Lee and Bernhard Sell                                                           |            |

|    | 14.1 Overview of FinFET Technology                                                        | 400        |

|    | 14.2 Unique Properties of FinFET Technology for RF/mm-Wave Design<br>Consideration        | 404        |

|    |                                                                                           | 404<br>404 |

|    | 14.2.1 Transistor Scaling and Performance                                                 | 404        |

|       | 14.2.2 Nonlinear Gate Resistance by 3D Structure                          | 406 |

|-------|---------------------------------------------------------------------------|-----|

|       | 14.2.3 Fin Self-Heating                                                   | 408 |

| 14.3  | Assessment of FinFET Technology for RF/mm-Wave                            | 410 |

|       | 14.3.1 Parasitics and RF Performance                                      | 411 |

|       | 14.3.2 Noise Performance                                                  | 412 |

|       | 14.3.3 Gain and Noise Matching at the mm-Wave Frequency                   | 414 |

| 14.4  | Design Methodology for RF/mm-Wave Performance Optimization                |     |

|       | with FinFET                                                               | 416 |

|       | 14.4.1 Wireless Design Consideration in Cascade Chain                     | 416 |

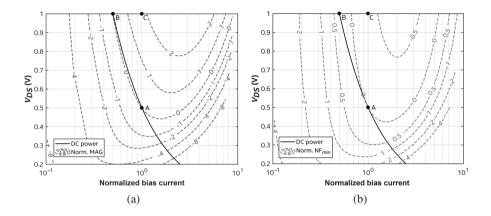

|       | 14.4.2 Optimizing NF with G <sub>max</sub> for LNA within Self-Heat Limit | 417 |

|       | 14.4.3 Gain per Power Efficiency                                          | 420 |

|       | 14.4.4 Linearity for Gain and Power Efficiency                            | 423 |

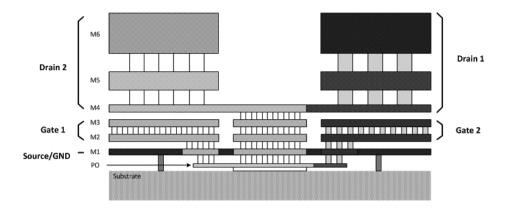

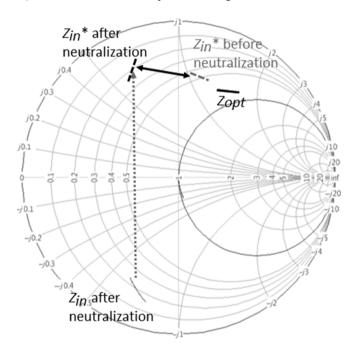

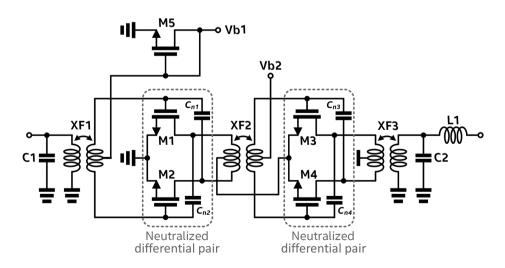

|       | 14.4.5 Neutralization for mm-Wave Applications                            | 425 |

| 14.5  | Design Example for an mm-Wave Amplifier with the Proposed                 |     |

|       | Design Methodology                                                        | 427 |

| 14.6  | Conclusion                                                                | 429 |

|       |                                                                           |     |

| Auth  | or Index                                                                  | 432 |

| Subje | ect Index                                                                 | 433 |

|       |                                                                           |     |

## **Contributors**

**Elad Alon** University of California at Berkeley, US

André Bourdoux Imec, Belgium

Lucas Albert Calderin Apple, US

Jan Craninckx Imec, Belgium

Tolga Dinc Kilby Labs, Texas Instruments, US

## Davide Guermandi

Imec, Belgium

**Payam Heydari** University of California, Irvine, US

**Gernot Hueber** Silicon Austria Labs, Linz, Austria

Harish Krishnaswamy Columbia University, New York, US

**Greg LaCaille** University of California at Berkeley, US

**Hyung-Jin Lee** Intel Corporation, Portland, US Thomas Lee Stanford University, US

Mohyee Mikhemar Broadcom Limited, US

Arun Natarajan Oregon State University, US

Ali M. Niknejad University of California at Berkeley, US

**Borivoje Nikolić** University of California at Berkeley, US

Kenichi Okada Tokyo Institute of Technology, Japan

**Aarno Pärssinen** Oulo University, Finland

Antonio Puglielli Zendar, US

Sameet Ramakrishnan Amazon, US

Leonard Rexberg Ericsson, Sweden

Patrick Reynaert KU Leuven, Belgium

Bodhisatwa Sadhu IBM T. J. Watson Research Center, US

**Bernhard Sell** Intel Corporation, Portland, US

**R. Bogdan Staszewski** University College Dublin, Ireland

**Piet Wambacq** Imec, Belgium and Vrije Universiteit Brussel, Belgium

## Rui Wu

Tokyo Institute of Technology, Japan

## Wanghua Wu

Samsung Semiconductor, US

## Yang Zhang

KU Leuven, Belgium

## Foreword

Around New Year's Day of 2002, the number of wireless subscribers exceeded the number of wireline subscribers for the first time in history, marking our becoming a wireless species. The number of wireless subscriptions continued to grow until by 2017 it had actually exceeded the population of the earth. By any measure, wireless has been one of the most spectacularly successful technologies in history. Consumers purchase five million cellular phones daily and use them to exchange one million information-free text messages every second. The average person now has instant access to the cumulative extracorporeal intellectual treasure generated by our ancestors over millennia. The cell phone allows us to order goods and services from all over the planet, at any time and from any place. The most potent sovereigns of prior centuries could not even dream of such capabilities for themselves, let alone for all of humanity. And yet we want more.

Given that virtually everyone with the ability to operate a cell phone now has one, it is natural to ponder what form *more* could possibly take. Predictions ("especially about the future") are notoriously unreliable and often absurdly humorous in retrospect, but perhaps in the history of wireless we may find useful clues about likely futures. After all, even when history doesn't repeat, it sure seems to rhyme, to paraphrase Mark Twain.

Wireless has evolved through three distinct ages, each characterized by its network topology. Station-to-station spark telegraphy found its niche in maritime communications, where it had no competition. The role of Marconi equipment (and an operator who lost his life) in saving over 700 passengers of RMS *Titanic* in 1912 testified dramatically to the transformation that wireless could bring. A transoceanic voyage would no longer be the equivalent of disappearing from the planet for the duration. Wireless telegraph equipment was installed so rapidly that thousands of ships and stations had been connected by the advent of World War I in this first age of wireless.

As revolutionary as was that first age, the station-to-station topology forced by the use of Morse code and complex equipment limited deployment to less than about 10,000 nodes - the sum total of the number of ships and stations. The next age of wireless happened almost by accident, driven by engineers who sought to convey the voice wirelessly. The unprecedented appropriation of *broadcasting* ("the spreading of seeds") from the lexicon of farmers speaks to the fierce velocity with which the technology took hold. The asymmetrical topology of broadcasting supported a large number of passive listeners with inexpensive and simple receivers, enabling programs to be heard by millions of people. This second age of wireless quickly transcended the kiloscale limits of spark-wireless to achieve megascale reach.

The Second World War introduced millions of soldiers to people-to-people wireless technology with walkie-talkies and other military communications devices. After returning to civilian life, they wondered why they couldn't have the same convenience that they had enjoyed during the war. Service providers such as AT&T in the United States responded to the demand by experimenting half-heartedly and often skeptically with people-to-people wireless communications for 30 years. Several nations finally began wide-area deployment of analog cellular systems throughout the 1970s and 1980s. Digital systems eventually replaced those early analog systems, and by 2013 voice traffic constituted only a minority of the bits conveyed; we had become a digital wireless species.

The evolution of wireless saw a three-order-of-magnitude jump in scale at each transition, from spark's station-to-station kiloscale to today's people-to-people gigascale connectivity. Thus having covered all possible permutations of *stations* and *people*, one might argue that wireless has reached the end of history. While that is certainly a possibility, an optimistic view is that it is an improbability. It is nonetheless sobering to observe that sustaining the evolution of wireless along historical trajectories would require an increase in connectivity to the terascale.

The much-hyped *Internet of Things* (IoT) has the potential to drive such an increase in connectivity, even though the name sometimes evokes images of one's refrigerator conspiring with the toaster against the blender. Since, for the moment at least, only humans have credit cards, any new age of wireless must present something of compelling value to people. The grandiose-sounding *Internet of Everything* (IoE) is sometimes used to distinguish this human-centered view from the more impersonal-sounding IoT.

The 5G wireless networks currently under development aren't betting solely on the IoE's success to justify deployment, but they are wisely accommodating the possibility. Whatever the future of wireless, tomorrow's networks will have to support vast increases in aggregate data rate, achieved in part by exploitation of the huge, untapped millimeter-wave spectrum and by the use of cells of ever-smaller radii. Recognition that millimeter-wave signals have considerable utility beyond communication has led to expectations that applications such as radar and other sensing, and perhaps even wireless power delivery to IoE devices, will be served as natural and inevitable consequences of 5G deployments. The smartphones and other conversants of the fourth age of wireless will thus surely possess advanced capabilities that will make today's devices appear primitive in comparison. This book provides a comprehensive guide to solving the challenging problems that stand between today and that glorious future.

#### Thomas H. Lee

## **1** Introduction

Gernot Hueber and Ali M. Niknejad

## 1.1 5G

A lot of the focus of this book is on 5G, so you may be wondering, what exactly is 5G? And, perhaps more importantly, how does it impact me as a circuit designer? Hopefully we can answer the first question in this chapter, and leave the rest of the book to address the second one.

## 1.1.1 What Is 5G?

The term "5G" has been around for a while as it is really a marketing term. People were talking about 5G even before anyone knew what 5G was going to be about. Even today, if you ask five different people, "What is 5G?" you may get more than five answers! Well, the name is naturally 5G because it is the "Fifth-Generation" mobile network standard. Ultimately, 5G will be defined by standardization bodies such as 3GPP (3rd Generation Partnership Project), and even then the concept of 5G will evolve. The reason that it's so difficult to pin down a clear definition for 5G is that it's going to be a worldwide network standard for the next decade, and there's a long wishlist of new technology elements that people want to see in 5G, and then there's the reality of building and deploying a new network and keeping costs and power consumption at a reasonable level. So 5G is a compromise between our dreams for the next-generation radio versus the reality of what is technologically feasible and economically viable.

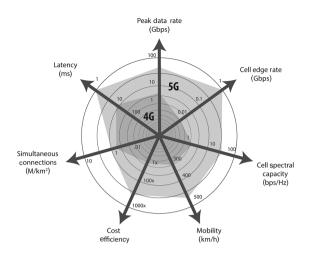

5G technology is positioned to address all of the shortcomings of 4G technology. In particular, people envision "everything in the cloud," which can offer a desktop-like experience on the go, immersive experiences (lifelike media everywhere), ubiquitous connectivity (intelligent web of connected things), and telepresence (real-time remote control of machines) [1]. To address these new application scenarios from a mobile device, the following "rainbow of requirements" shown in Figure 1.1 have been defined: (1) peak data rates up to 10 Gbps, (2) cell edge data rate approaching 1 Gbps, (3) cell spectral efficiency close to 10 bps/Hz, (4) Mobility up to 500 km/h, (5) cost efficiency that is 10 to 100 times lower than 4G, (6) a latency of 1 ms, and finally, and perhaps most importantly, (7) over 1 M simultaneous connections per  $km^2$  [1,2].

Before we dive into the details, it's useful to have a very brief history lesson.

Figure 1.1 The 5G rainbow of requirements, adapted from [2].

Figure 1.2 Evolution of humankind alongside wireless communication technology [3].

## 1.1.2 A Brief History of the Gs

Some of us are old enough to remember the days of brick-sized phones and analog mobile communication, the so-called 1G era and the Advanced Mobile Phone System (AMPS), first deployed in 1979 (see Figure 1.2). The system was analog and operated originally in the 850 MHz frequency band. The channel bandwidths were only 60 kHz and it was intended for voice communication. One important distinction to note is that 1G systems were circuit switched, so once a call was activated, the spectrum was allocated to a user, even if both sides of the link were silent.

In the early 1990s, the 2G generation took over and offered digital communications for the first time, including the ability to use Time Division Multiple Access (TDMA). In most parts of the world, 2G and the term GSM (Global System for Mobile communications) were synonymous, which used 200 kHz per channel, and Gaussian Minimum Shift Keying (GMSK) modulation (constant envelope) for power amplifier (PA) efficiency. But in addition to the GSM standard, a second-generation AMPS standard

called Digital AMPS (D-AMPS), also referred to as TDMA, was in operation (IS-54 and IS-136). At the same time, Qualcomm was actively selling a new radio access technology known as Code Division Multiple Access (CDMA), and these radios were standardized as IS-95.

There were some 2.5G systems that used packet switching, known as General Packet Radio Service (GPSR), as opposed to circuit switching, which allowed the system to offer more efficient spectral access. This meant that more time slots could be allocated on demand, and the latency and data rate depended on the number of users connected to a base station. By today's standards, 2.5G systems were dog slow, topping in at 50 Kbps. At first no one was really using mobile for data, and this didn't seem to be an issue. But the increasing popularity of mobile communication drove the need for more bandwidth and more speed. This is where the 2.75G standard evolved and offered EDGE (Enhanced Data Rates for GSM Evolution), offering theoretical speeds of 1 Mbps, by using 8-PSK encoding (three bits per symbol).

Interestingly, the first iPhone was released in 2007, 16 years after the introduction of 2G, and it was still a 2G device. For those of us lucky enough to have owned a first-generation iPhone, the experience was both amazing and also tortuous because of the slow network speeds due to 2G limitations and also due to the fact that in dense urban environments, everyone was all of a sudden trying to access the network for Internet connectivity at the same time. These early smartphones, especially the iPhone, were heavy users of data, and they really showed the world that the 2G network was not good enough. Other devices at the time were already using 3G technology, which came in many shapes and sizes.

In the late 1990s and early 2000s, the 3G networks started to operate and offered improved data rates by increasing the bandwidth of channels (up to 5 MHz) and adopting spread spectrum techniques and higher-order constellations (16- and 64-QAM) and multiple-input and multiple output (MIMO) techniques. The Universal Mobile Telecommunications Service (UMTS) radios were introduced as hybrid 2G/3G UMTS/GSM radios. Sometimes these systems were referred to as W-CDMA systems, due to the use of a wideband code division multiple access technique. Data rates increased to 384 Kbps in the original systems, and evolutions pushed the data rates higher to Mbps regions with High Speed Packet Access (HSPA) and HSPA+ offering up to 168 Mbps in downlink and 22 Mbps in the uplink. The adoption of multiple bands meant more complex front-end circuitry, wider bandwidths, and therefore more linearity to handle more complex modulation schemes. In parallel, the CDMA2000 standard (IS-2000) offered peak data rates of 14.7 Mbps using 1.23 MHz of channel bandwidth. Unfortunately, the CDMA2000 and UMTS/HSPA radios were standardized by different committees and were not interoperable, making phones not only region-specific but also carrier-specific.

Today we are living and fully immersed in the 4G world of LTE, or Long Term Evolution, the "winner" technology that is ubiquitous worldwide. One of the requirements for 4G was to offer over 100 Mbps of peak data rate for highly mobile access and approximately 1 Gbps for low mobility access. The Samsung Galaxy Indulge was the world's first LTE smartphone starting on February 10, 2011 [1]. To move toward these lofty goals in power transfer and low latency, LTE networks were all Internet Protocol (IP) packet switching, employed very dynamic network architectures for optimum sharing of network resources, offered scalable bandwidths from 1.4 MHz up to 20 MHz, and distributed these resources on demand using Orthogonal Frequency Division Multiple Access (OFDMA) [4]. The spread spectrum techniques widely used in 3G systems were abandoned in favor of OFDMA, or the division of a wide bandwidth into smaller bands, modulation of the subcarriers at a much lower rate, and the use of a cyclic prefix in the guard band, thereby circumventing frequency-dependent fading and intersymbol interference. Using many subcarriers also allows the base station to optimize resource allocation by allocating spectrum resources in both time and frequency slots. More efficient turbo codes and MIMO techniques also improved the link quality.

One well-known pitfall with OFDMA is that the composite multicarrier signal has a very high peak-to-average power ratio (PAPR), which spells disaster for power amplifiers, requiring high back-off and linearization. These issues are well known to the power amplifier community as WiFi networks adopted OFDM (Orthogonal Frequency Division Multiplexing) as early as 1999 and the introduction of 802.11a. To circumvent this high PAPR, and single-carrier FDMA (SC-FDMA) for the uplink reduces PAPR. This slightly complicates the transmitter and requires frequency domain equalization in the receiver.

While most 4G systems converged on LTE, providing compatibility in theory, in practice the number of LTE bands exploded covering from 450 to 3600 MHz and both frequency division duplex (FDD) and time duplex (TDD) access. This meant that designing a "worldwide" LTE phone would be a formidable task due to the number of different front-end components required to cover disparate frequency bands and access modes (FDD versus TDD). LTE-Advanced (LTE-A) is an extension of LTE with new features including up to  $8 \times 8$  MIMO and 128 quadrature amplitude modulation (QAM) in the downlink and carrier aggregation of contiguous and noncontiguous spectrum allocations, allowing up to 100 MHz of aggregated bandwidth. This means a device with LTE-A has a theoretical peak download data rate of 3 Gbps [5]. While this rate is impressive, in practice most users never reach these peak data rates.<sup>1</sup>

As evident in this brief history, each generation of mobile standards has embraced the latest advancements in communication theory and technology, in particular advances in coding, multicarrier modulation and wider bandwidths, and MIMO techniques to enable ever-increasing data rates and more efficient and dynamic networks. Each generation lasted about a decade, and it is a small miracle today that we can all enjoy watching our favorite cat videos from virtually anywhere on the planet.

#### 1.1.3 Do We Need 5G?

So why do we need 5G? LTE and WiFi are amazing technologies that have served us well. Will the investment in a new network pay off? First, let's consider the new generation of users of wireless technology. A typical 12 year old today was born with

<sup>&</sup>lt;sup>1</sup> The coeditor of this book has obsessively tested his phone all over the Bay Area and topped out at 162 Mbps downlink and 43.5 Mbps uplink.

a smartphone or tablet in her vicinity for most of her life. She may have never even experienced Internet blackout as a whole generation of parents replaced the TV with the smartphone/tablet as the de facto caregiver. The TV was limited in mobility whereas a smartphone can be carried anywhere and offer not only videos, but countless games and other forms of entertainment that only this new generation can understand.<sup>2</sup> This generation has a different relationship with bandwidth because they constantly stream video. Students prefer watching lectures online, especially because they can slow down and speed up the lecture and look up things while watching. To give a simple but illustrative example, the coeditor of this book was telling his daughter about paper and how it's actually a fibrous material that looks like a thin layer of spaghetti under an electron microscope. Before finishing his sentence, his daughter was watching such videos on YouTube. What surprised the coeditor was that she went directly to YouTube rather than to an Internet search engine or to Wikipedia.

Now let's try to imagine what a kid will do in 10 years when trying to understand something new, such as an internal combustion engine works. Hopefully this will be an ancient relic that arouses her curiosity since electric propulsion will completely displace such engines. She'll slip on her virtual reality or augmented reality goggles, or perhaps use a holographic projector to show the engine. She'll be able to rotate the engine, look at the different parts, and then with a simple gesture, she'll be able to blow out the engine into thousands of parts. She can then put back the engine and just look at a few components, say inside the engine block, and play with the pistons and see how they move up and down and generate a rotational motion through the crank shaft. She'll be able to learn a tremendous amount in a short period of time. Clearly, this data will have to be downloaded from the Internet and played back in real time. Maybe she's repairing a classic automobile and needs to see the 3D images again while she's in the garage. Remember that a single base station will need to serve hundreds or thousands of curious kids, all at the same time.

In certain situations, the demands on the network will explode. Imagine a classroom full of thousands of students learning anatomy. The professor will have a virtual cadaver in front of him and he'll be making incisions and demonstrations of different parts fit together. Every student will have his or her own virtual cadaver as well. In fact, there's no need to use an inanimate body, because a virtual body that is alive and moving is much more interesting, for example to understand how muscles and connective tissue work together to enable different motions. In this scenario, we have thousands of simultaneous three-dimensional (3D) high-definition (HD) connections, all in the same geographic location. This is clearly beyond the capabilities of both WiFi and 4G networks today.

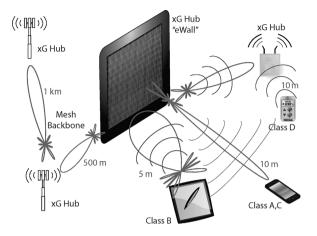

At the Berkeley Wireless Research Center (BWRC), we looked at these issues and considered a blank slate to imagine what should the next generation of wireless look like. In December of 2013, we codified our vision with the xG network, shown in Figure 1.3. Our vision is for a new network that utilizes a massive number of antennas in access points to allow a high degree of spatial multiplexing to many different disparate devices,

<sup>&</sup>lt;sup>2</sup> Such as watching others play video games or watching someone playing with slime.

**Figure 1.3** The BWRC "xG" vision for the next-generation wireless communication system (December 2013).

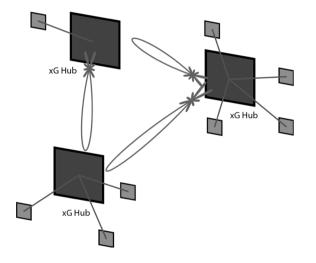

**Figure 1.4** Wireless backhaul using phased arrays and mesh networking can reduce the cost of deployment of a 5G system by obviating the need for fiber connectivity.

from cell phones and tablets to Internet of Things (IoT) devices. Multiple RF and mmwave frequency bands are used in a complementary fashion to form both sharp and broad beams. Also, most importantly, these access points self-backhaul by forming a hierarchical wireless mesh network (Figure 1.4), avoiding the need to use cables or fiber to form the backhaul network. In such a way, the network can grow organically to serve the demands for wireless traffic. The access point can wake up, identify other nodes in the network, and begin routing traffic on demand, with links going up or down in a dynamic fashion, much like the original vision for the Internet and the need for packet switching. In parallel, people started dreaming of 5G and what it should encompass. Many people came to the realization that to serve these visions, we need to utilize higherfrequency bands to realize higher spectral efficiencies and to circumvent interference, and the idea that 5G would also operate in the mm-wave bands was born.<sup>3</sup>

## **5G Wishlist**

Given this xG vision, which is more or less the same as what people were thinking for 5G, let's enumerate our wishlist a bit more carefully. Are today's networks fast enough both in terms of speed of transmission and latency per user? While a lot of progress has been made on speed, even exceeding 1 Gbps, these improvements are mostly for marketing and don't bear out in practice. But nevertheless, being able to get a mobile wireless connection over 10 Mbps is quite impressive and certainly sufficient for many applications such as video. The problem is that many times we cannot get sufficient coverage and we are all too familiar with video streams coming to a screeching halt at just the right moment. The other issue with today's networks is the latency is typically tens to hundreds of milliseconds long, and sometimes even longer. The latency is also unpredictable, making it difficult to design a closed-loop control system. For this reason, many applications that could benefit from wireless technology have not embraced wireless. Examples include industrial control, semiautonomous driving, multiuser gaming, and virtual reality and augmented reality devices driven from the cloud.

While speed is definitely a great marketing specification, another revolution is under way, the proliferation of low-cost devices with wireless connectivity. This is the wellknown and much anticipated IoT revolution, which requires very small footprint and low-power wireless connectivity, and in most cases the speed is not an issue. More important than speed is the power consumption. Today people are adding Bluetooth, Bluetooth Low Energy (BTLE), Zigbee, WiFi, or other radios for wireless connectivity. These radios are short range and cannot actually connect to the Internet without a nearby access point (such as a WiFi router connected to the Internet). Why not just put LTE radios in such devices? The problem with LTE is cost and power consumption, and a lack of a clear business model. For example, many smart watches today have an LTE radio inside but suffer from poor connectivity and require frequent recharging, and each device requires registration with the carrier (and a not-so-insignificant fee per month). Clearly this does not lend itself well to IoT, where we imagine thousands of devices operating on small coin cell batteries.

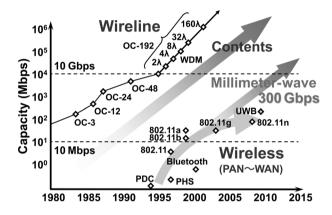

This brings us to another point. WiFi technology has advanced tremendously in the past 20 years, and for a long time there was a clear boundary between mobile carrier connectivity and wireless connectivity with WiFi and Bluetooth. But today the boundary is blurring, and in many cases these technologies compete. In a crowded café, dozens of users are streaming video from the Internet and one may find that LTE outperforms WiFi. LTE technology operates in licensed spectrum and interference is managed much better than in WiFi unlicensed spectrum, where the access point may only have control over a subset of devices operating in the same band. In many ways, both WiFi and

<sup>&</sup>lt;sup>3</sup> Samsung, "Pioneer in 5G Standards, Part 1: Finding the 'Land of Opportunity' in 5G Millimeter-Wave." http://bit.ly/2GBDoiA.

mobile standards have converged, for example the use of OFDM to manage equalization in a wideband channel, power control for interference mitigation, similar modulation and coding schemes, and MIMO. LTE even now operates in unlicensed bands, and carriers are encouraging users to use the WiFi infrastructure to relieve traffic demands on the operator. So why should we have two standards if they are so similar? While it's unlikely that WiFi and LTE will ever merge into one standard (politics alone will prevent this from happening), we could wish for more interplay and compatibility between the radios. Too often we are frustrated by our wireless devices not connecting to the Internet only to find that the WiFi has taken over without truly connecting to the Internet. Many users have to actually manually shut off their WiFi on a daily basis to prevent their phones from connecting to a weak network. The situation has worsened because traditional broadband carriers are trying to compete with the wireless carriers by deploying citywide outdoor WiFi networks.

All of these problems arise because today's mobile networks are simply not up to the task of serving the exponentially growing needs of our modern devices. The spectral capacity of today's wireless networks are in fact operating close to Shannon capacity limits, and MIMO techniques are not as effective in outdoor channels (see Chapter 3). In dense urban environments, this is especially problematic because of high population densities (about 7,282 people in a square kilometer in San Francisco). If 10% of the population is actively watching videos at a given time in a given square kilometer (25 Mbps per HD stream), then the base station has to have a capacity of over 18 Gbps. To serve that much data with a 100 MHz swath of spectrum translates into a spectral efficiency of 180 bits/Hz, which is impossible without enormous signal-to-noise ratio (SNR) in a single channel scenario (not using MIMO). Base stations could be deployed over increasingly smaller areas to solve this problem, but then we are plagued with interference and cost barriers. On the other hand, massive MIMO demonstrations have already showed nearly 100 bits/Hz of spectral capacity in a multiuser MIMO scenario, which is a technique that can improve the aggregate capacity of a system rather than the per-user capacity, and this is an exciting technology on our wishlist for 5G. The other approach is to just go to higher carrier frequencies where wider bandwidths make it easier to serve high data rates. Higher frequencies have propagation issues but offer the ability to use beam-forming to reduce interference as well.

Finally, let's consider the enormous cost to deploy a new network, especially a network with an order of magnitude more base stations to serve dense urban environments. Such an investment should pay off in less than a decade to allow the operators to be profitable. This means that the cost of base stations has to go down, especially in terms of rents on property, backhaul access, and electricity costs. Since mm-wave radios are shorter range, one can anticipate a  $10 \times$  densification of base stations, which must be accommodated by a  $10 \times$  reduction in building a base station. For this to happen, wireless backhaul is a must, as many locations cannot be served by fiber without tearing up the streets and installing new access. Also, wireless backhaul using a phased array, rather than a dish, is clearly advantageous to reduce the setup cost for a new base station. A phased array can dynamically find other nodes and point the beam appropriately, whereas a fixed point-to-point link requires precision antenna alignment. Even a massive

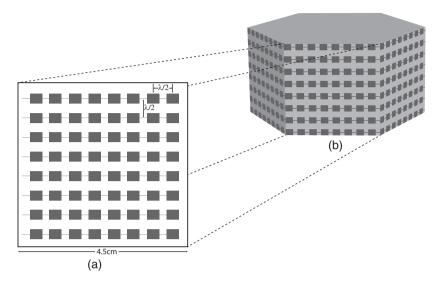

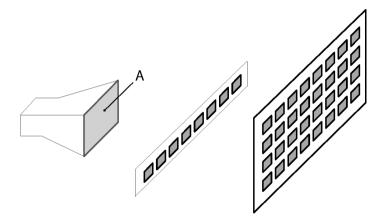

**Figure 1.5** An array of 64 patch antennas only occupies an area of 4.5 cm by 4.5 cm as shown in (a). In (b), an array of such panels forms a four-sector base station that can serve thousands of users simultaneously using multiple spatial beams.

array of antennas in mm-wave bands does not occupy much area. Take a linear array consisting of 64 elements, or antenna subarrays, each with 8 elements, as shown in Figure 1.5. Even at 28 GHz, one of the lowest frequency mm-wave bands, the size of the array is  $8 \cdot \lambda/2 \times 8 \cdot \lambda/2$  or about 4.5 cm  $\times$  4.5 cm. A base station may consist of a half a dozen of such panels, which means the entire base station could fit in a cube with an edge.

## The Cloud

Today we have an enormous amount of data moving from edge devices (say your mobile phone) all the way up the cloud, a room full of servers running the applications. These data have to move back and forth, and it means a lot of data transport over hundreds of kilometers and also a lot of latency. For example, using the web service cloudping.info, the measured ping speed from a mobile phone to the Amazon Web Services is around 50 ms, whereas the ping speed to the carrier is only 25 ms. Clearly any applications such as gaming or augmented reality require millisecond delays, both for health concerns (to avoid making people dizzy) and to make the experience more real. If we could run applications much closer to edge devices, we could greatly improve the latency. This is exactly what people are proposing in industry, putting the servers in base stations, or rather moving base stations into server racks. To keep costs low and allow base station densification, the base station is split into a remote radio head and then backend processing is moved offsite into a server rack. This architecture has other benefits, such as making the network more software defined and flexible. Traffic to/from remote radio heads can be managed on the fly, serving demand (a stadium during the game) when and where it's needed.

Recently there's a lot of buzz around the concept of full duplex communication. Full duplex means a radio can transmit and receive at the same time, in the same bandwidth. Traditionally this was achieved with a circulator or isolator, or a nonreciprocal element. A circulator is a three-port device that allows both the PA and low-noise amplifier (LNA) to be connected to the antenna without any interference (or only a small amount of the transmitter signal leaks into the receiver). A four-port hybrid can do the same thing, at the cost of insertion loss. A practical circulator has loss too, but there's no fundamental limit to how low this loss can be. On the other hand, more importantly, circulators are bulky and narrowband, and cannot be integrated into a chip due to the need for nonlinear magnetics. Recently the coauthors of this book have demonstrated new CMOScompatible architectures for circulators, and these are described in detail in Chapter 4. Another active cancellation approach, which is applicable to novel full-duplex systems and also traditional frequency division duplex (FDD) systems is presented in Chapter 5. FDD is common today and allows simultaneous transmit and receive in two nearby bands by the application of a sharp filter, or duplexer, to provide isolation. These filters are also band-specific and difficult to integrated into CMOS. This chapter will take a different route and use active impedance synthesis to cancel the transmit signal in the receive band.

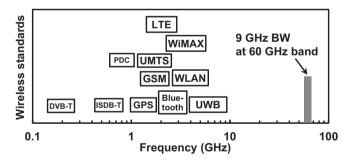

While much of the buzz around 5G is in the new mm-wave bands, such as 28 GHz and 39 GHz, the 60 GHz band will likely play an equally important role as an unlicensed spectrum, much as WiFi today plays a complementary (and sometimes competing) role to LTE. The amount of bandwidth available in the 60 GHz band is enormous, and we are witnessing multiband radios that can pump tens to hundreds of gigabytes per second through this spectrum. This capability will enhance local area networks and provide backhaul mesh networking to 5G systems. In Chapter 8, we describe the latest chipset, which can push the limits of CMOS in the 60 GHz band to demonstrate record data transfer speeds.

## 1.2 Radar

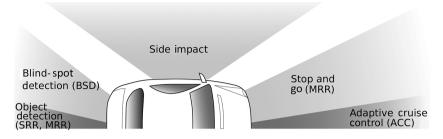

Advanced Driver Assistance Systems (ADAS) are all systems to support the driver for safety and enhance driving convenience. There is a strong and important focus on safety, as many if not most accidents are a result of human behavior or error. Consequently, the ultimate goal of ADAS is to avoid any kind of accidents or collisions, by facilitating automated systems ranging from obstacle detection (e.g., vehicle, parking, pedestrian, etc.) to traffic sign detection and driver monitoring (e.g., drowsiness) or communication (car-to-car, car-to-infrastructure; see Figure 1.6). A key technology of ADAS is the detection of any kind of obstacles by specialized radar systems.

The use cases for automotive radar are diverse and include the following scenarios that demand specific requirements on the detection device:

Adaptive cruise control (ACC) is applicable in normal driving conditions to adapt the drive speed to the cars ahead as well to detect obstacles in the far distance to avoid

Figure 1.6 Future ADAS systems make use of multiple dedicated sensors for dedicated use-case scenarios and as part of a *sensor fusion*.

any accidents. This is the use case with the most demanding requirement in SNR and range (up to  $\sim$ 200 m). ACC is addressed by long-range radar (LRR) 77 GHz radar systems at the front of a vehicle.

- Blind spot detection (BSD) is a feature to detect other vehicles located to the driver's side and rear with the purpose to warn the driver of vehicles hardly visible and, in turn, to avoid potential collisions. With a range requirement of up to  $\sim$ 20 m, both, 24 GHz and 77 GHz are applicable.

- Short-range radar (SRR) is covered by 24 GHz systems located around the car (front, rear, side, or all four corners) and are used, e.g., for BSD, stop-and-go, or parking assistant applications, all of them at lower driving speed and lower total range (< 20 m)

- Medium-range radar (MRR) is used for BSD as well as for stop-and-go scenarios, with limited range (up to 40 m). Sensors are, depending on the specific use case, mounted around the car (four corners) for 24 GHz systems. However, 77 GHz will be used for medium range as well.

- Long-range radar (LRR) is the radar technology (77 GHz) that is applied for ACC. The sensors are mounted in the front of the vehicle to allow detections of other vehicles or obstacles ahead.

As of today's developments and available products, there are dedicated solutions that are highly optimized for the specific scenarios. Looking into the next generations, following a holistic approach, it is expected to see higher complexity by combining individual techniques into a *sensor fusion*. Consequently, specific dedicated solutions that are highly optimized for a specific purpose are combined (e.g., LRR, LiDAR, cameras) such that an extensive coverage of all use cases can be achieved. In turn, the challenge for sensor fusion is the real-time data aggregation of multiple sensors into a single holistic ADAS system.

Though currently 24 GHz [7–9] car radar solutions have been widely deployed, in current new designs 77 GHz is used [10–12]. However, it shall be noted, that regulation bodies are considering to allow for additional frequency bands beyond the 100 GHz, e.g., 134/136–141 GHz, and the European Technical Standards Institute (ETSI) is reviewing ultrawide band (UWB) radio determination applications within the frequency range between 120 to 260 GHz [13].

| Parameter                                                      | Value (target) | Value (max) | Unit |

|----------------------------------------------------------------|----------------|-------------|------|

| Range <i>R</i>                                                 | >100           | 250         | m    |

| Range resolution $\Delta R$                                    | 0.25           | 100         | m    |

| Speed resolution $\Delta v$                                    | 5              |             | km/h |

| Antenna gain Gant                                              | >10            |             | dBi  |

| System sensitivity <i>RX</i> <sub>sens</sub>                   | <70            |             | dBm  |

| Tx effective isolated radiated power<br>(EIRP) (77 GHz/79 GHz) | 25             | 50/33       | dBm  |

| Bandwidth BW (77 GHz/79 GHz)                                   | 0.8/2          | 1/4         | GHz  |

Table 1.1 Requirements for automotive radar systems.

**Table 1.2** Requirements for automotive long range radar receivers [14,15].

| Parameter                                      | Value | Unit |

|------------------------------------------------|-------|------|

| Stopband attenuation                           | >65   | dB   |

| Spurious-free dynamic range $(SFDR)^a$         | < -70 | dBc  |

| RX chain gain (RX,in to BB)                    | 70    | dB   |

| Overall noise figure                           | ~13   | dB   |

| Effective number of bits (ENOB) (at the        | >12   | bit  |

| BB-interface)                                  |       |      |

| Minimum input signal <i>P<sub>RX,min</sub></i> | -100  | dBm  |

| SNR <sub>min</sub>                             | 16    | dB   |

<sup>*a*</sup> Including intermodulation products ( $P_{in}$  at -20 dBm).

System-level specifications are shown in Tables 1.1 and 1.2 with a focus on range and speed resolution, and some key specifications for receivers and transmitters are given in Tables 1.2 and 1.3, respectively.

From a silicon technology perspective, there are two main trends. First technology widely used is SiGe BiCMOS. Advantages of SiGe BiCMOS include the developments of novel technologies with high  $f_{max}$  for currently available  $f_{max} = 500$  GHz to higher  $f_{max} = 700$  GHz and beyond is ongoing [16–20].

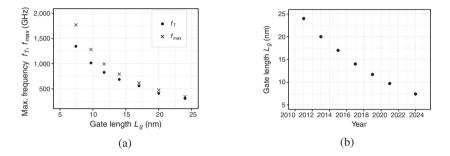

Alternatively, and in scope of monolithic integration with signal processing and digital control, is to use CMOS technology [21–23], which is a key advantage of CMOS. The development and predictions of CMOS available gate-length and maximum frequency is shown in Figure 1.7.

Another key advantage of CMOS technology is its ability to use the digital logic in a monolithic integration. Hence, the RF transceiver can be perfectly integrated with the baseband and application processing units, which allows highly efficient codesign of the RF, baseband (BB), and application processor (AP) and their interaction while peripheral parts (e.g., power management unit (PMU)) can be shared. This approach benefits from the increase of digital logic and static random-access memory (SRAM) transistor density increasing from 9,725 Mt/cm<sup>2</sup> (CMOS 15 nm half-pitch, 2018), 15,437 Mt/cm<sup>2</sup> (CMOS 11.9 nm half-pitch, 2020), to 24,505 Mt/cm<sup>2</sup> (CMOS 9.5 nm

| Parameter                                | Value | Unit           |

|------------------------------------------|-------|----------------|

| Phase noise <i>PN</i>                    | -94   | dBc/Hz at 1MHz |

| Frequency ramps $T_{ramp}$               | 20    | μs             |

| Frequency range $\Delta f$               | 2     | GHz            |

| Antenna gain Gant                        | 20    | dBi            |

| Minimum output power P <sub>TX,min</sub> | 10    | dBm            |

Table 1.3

Requirements for automotive long range radar transmitters based on [14,15].

**Figure 1.7** CMOS scaling as per the International Technology Roadmap for Semiconductors (IRS) [25] with (a) the expected  $f_T$  and  $f_{max}$  and (b) the projected RF-CMOS nodes.

half-pitch, 2022), considering the microprocessor unit (MPU)/application-specific integrated circuit (ASIC) MPU/ASIC technology roadmap data [24].

## 1.3 A Circuit Designer's Perspective

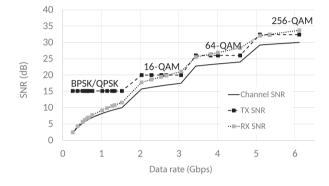

So we have a long wishlist for 5G, radar, and communication devices, and we are seeing many of our wishes coming to fruition in the standards bodies. The focus of this book is of course more on the circuits rather than the application. But we cannot design circuits without understanding the big picture first. This is why we start the book with an introduction to the system aspects of 5G (Chapter 2) as well for radar (Chapter 7). We also discuss the technology behind beamforming, MIMO, and massive MIMO in Chapter 3, phased arrays (Chapter 6), and full-duplex operation (Chapters 4 and 5). The rest of the book delves into circuit design details, including important topics related to frequency synthesis, power generation, and phased arrays. To achieve higher data rates, the industry has embraced more complicated modulation schemes such as 16-QAM, 64-QAM, and even 1024-QAM in 802.11ax. This requires extremely linear transmitters and receivers, and error vector magnitude (EVM) degradation will come from every source, especially the voltage-controlled oscillator (VCO)/phase-locked loop (PLL). High-frequency mm-wave VCOs are usually designed in stages, including a frequency multiplication stage and a more

traditional PLL. But due to the high multiplication ratio from the crystal oscillator (XTAL), e.g., from 10 MHz to 28 GHz means the phase noise increases by nearly 70 dB, requiring careful optimization of the synthesized signal. The VCO will likely have lower noise than the multiplied reference, so the VCO design, the PLL loop bandwidth, and carrier recovery strategy require cooptimization. Many chapters of this book are dedicated to the understanding of these issues, in particular VCO design in Chapter 12, frequency synthesizer design in Chapter 10, and the all-digital PLL approach covered in Chapter 11.

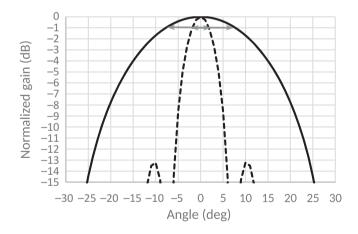

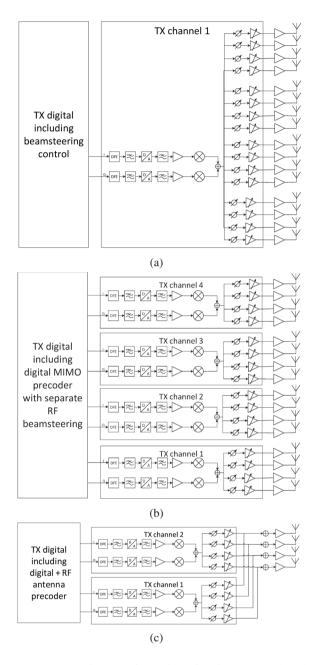

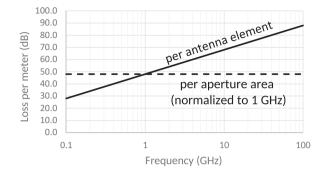

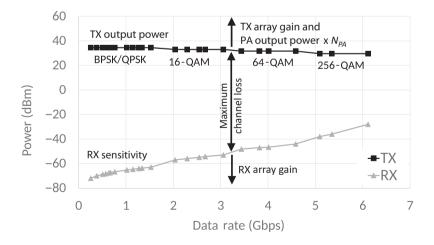

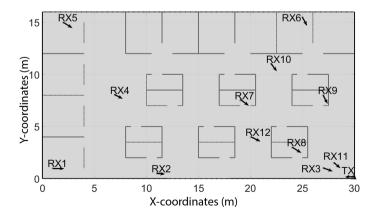

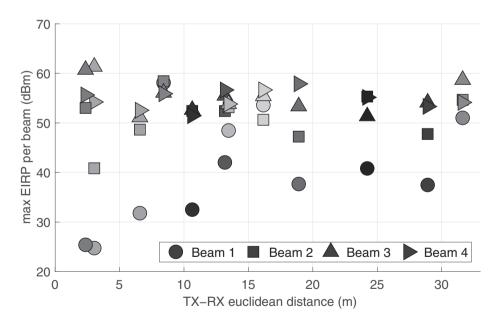

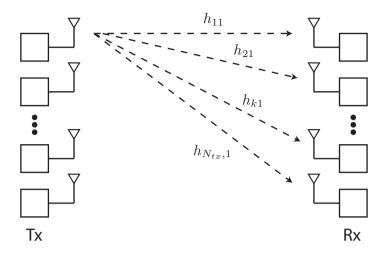

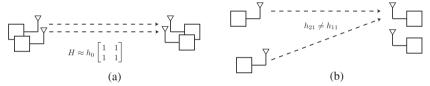

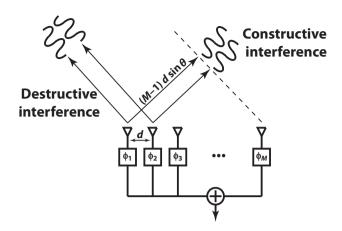

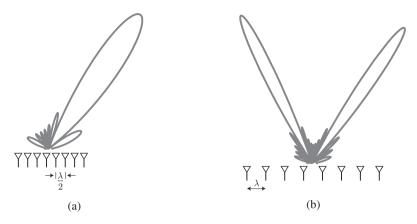

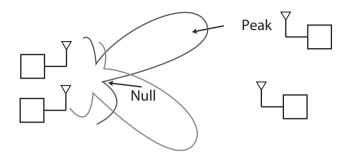

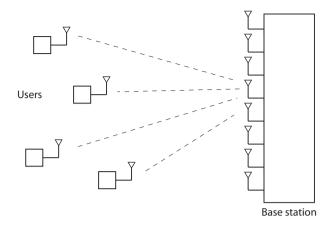

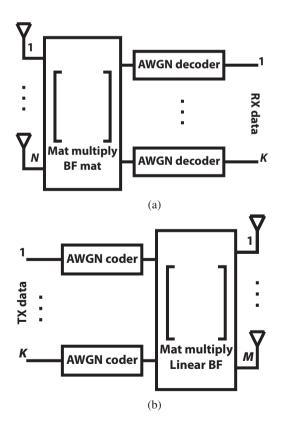

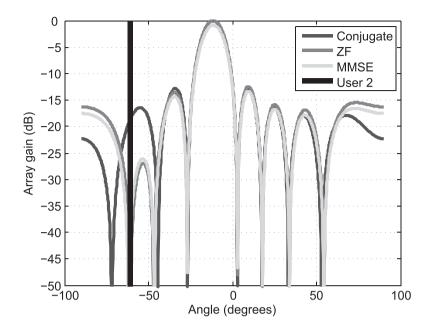

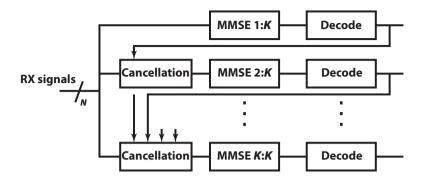

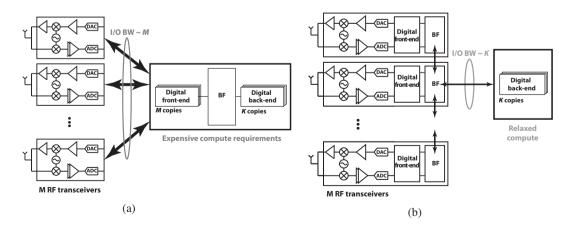

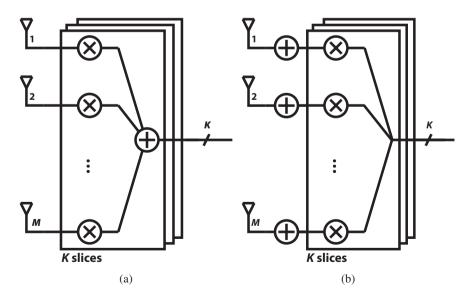

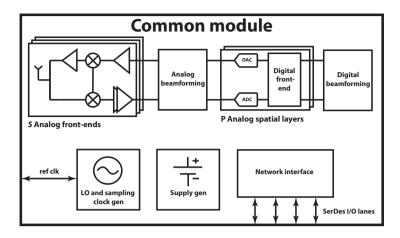

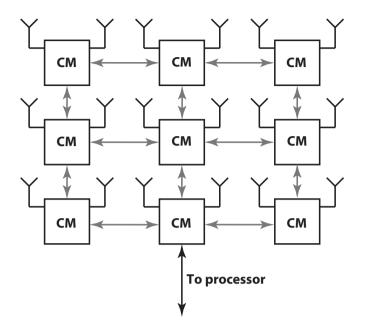

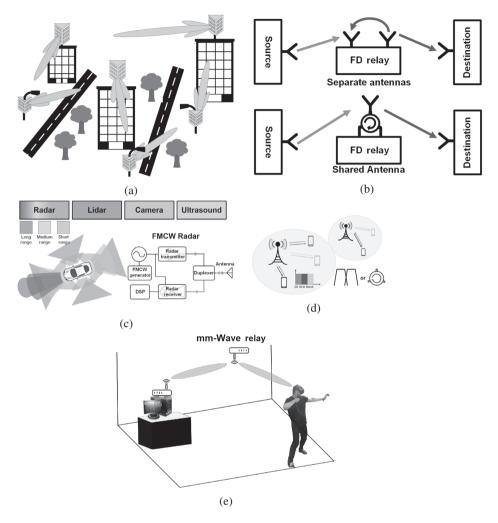

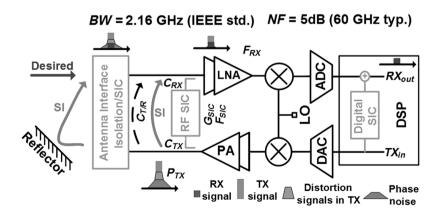

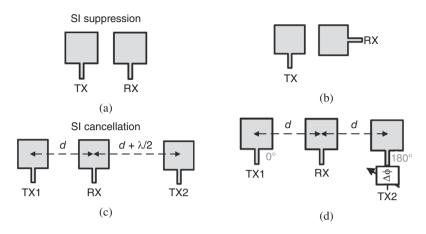

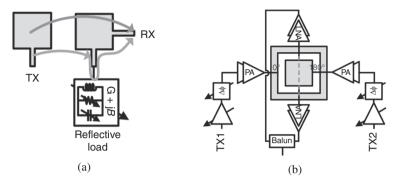

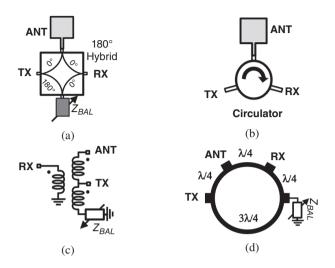

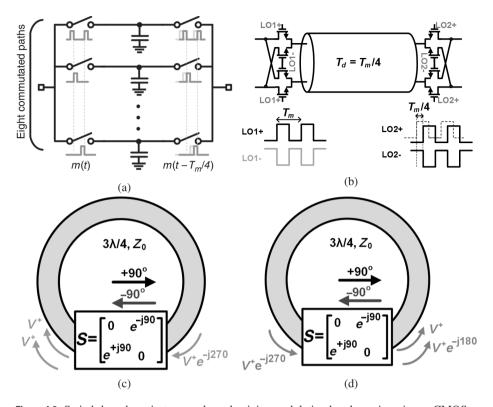

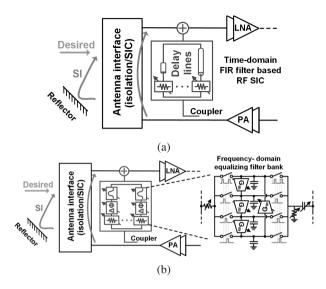

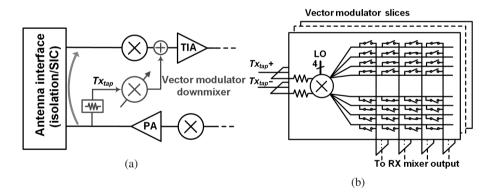

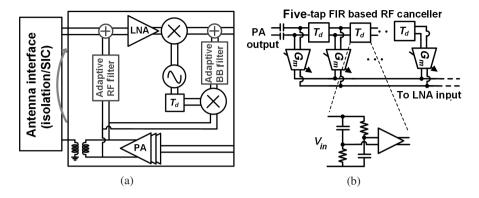

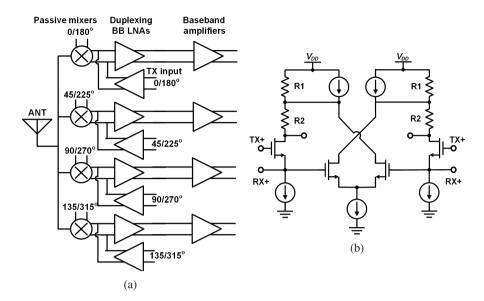

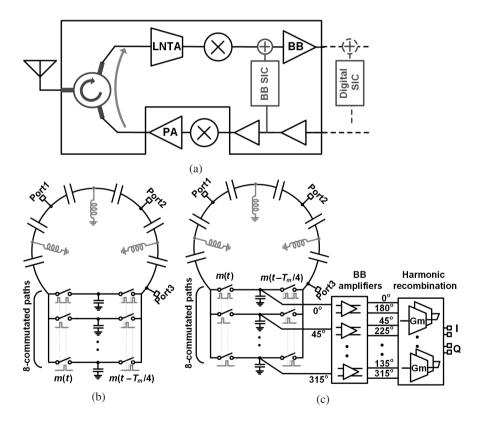

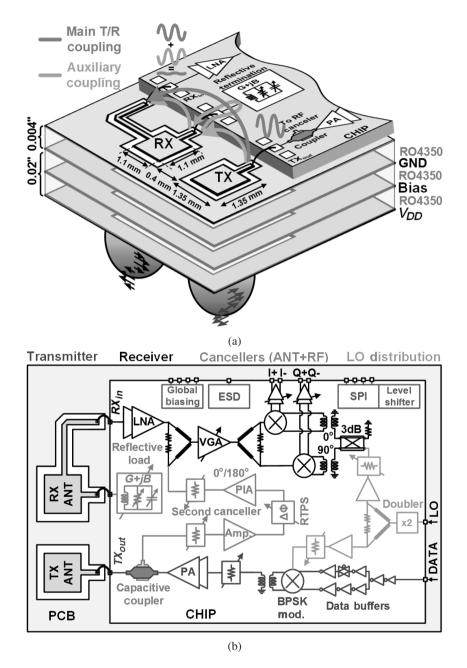

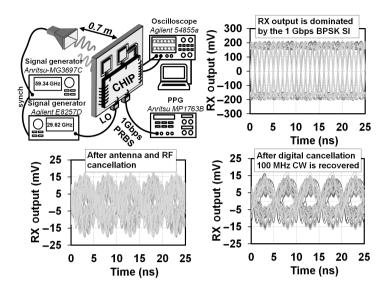

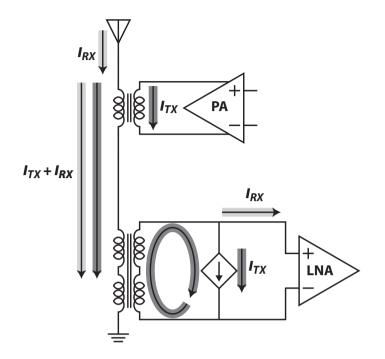

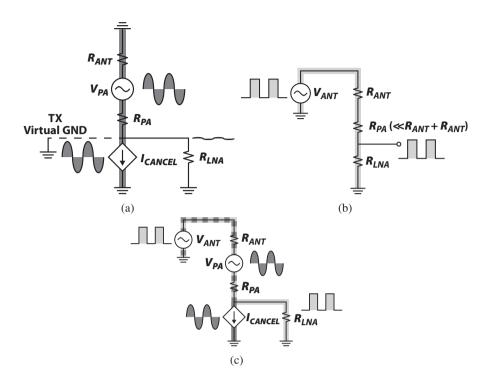

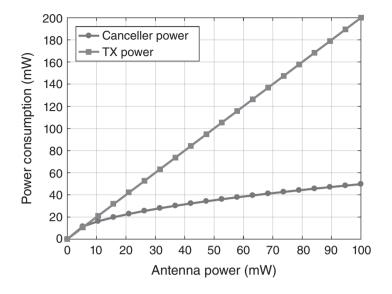

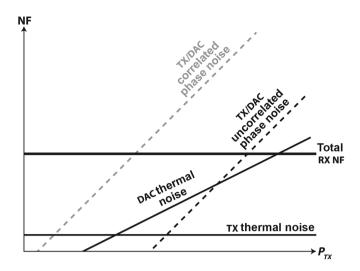

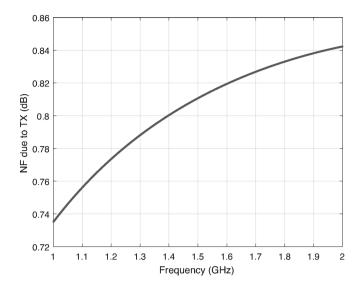

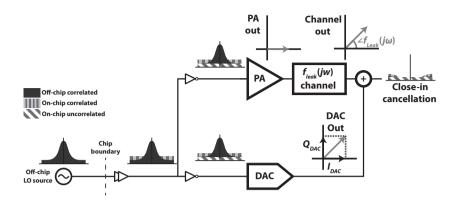

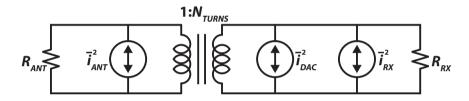

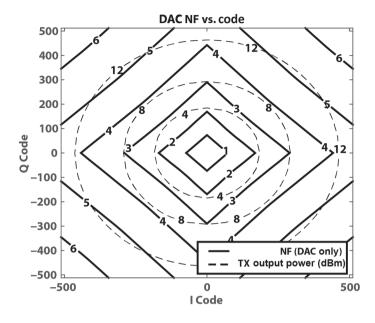

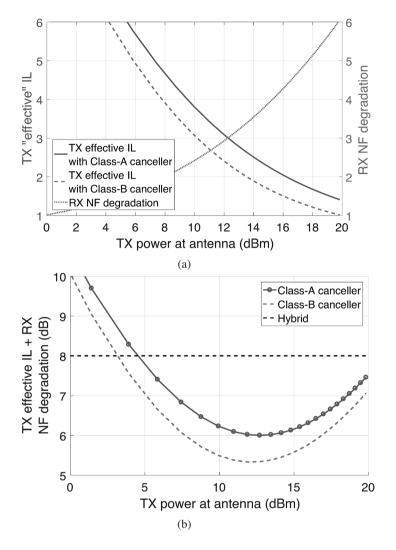

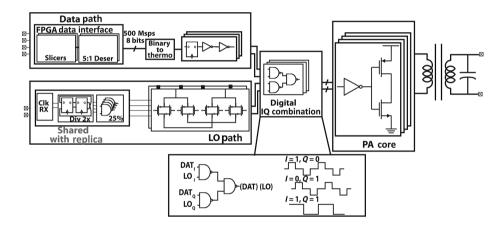

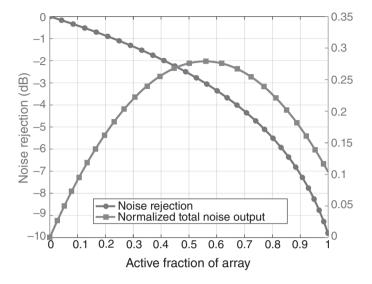

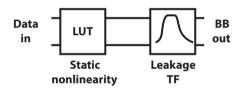

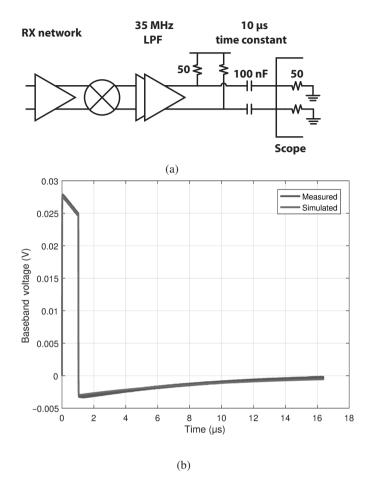

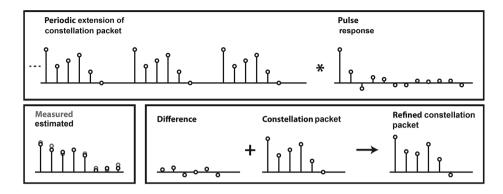

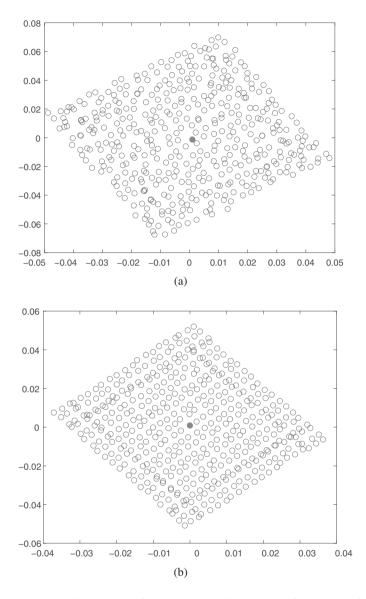

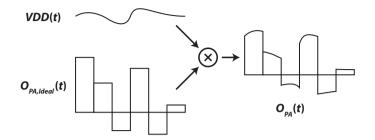

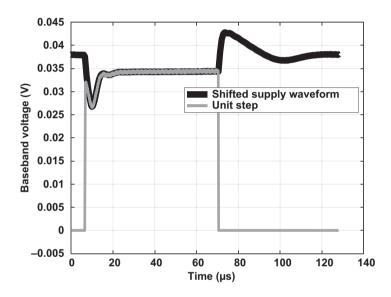

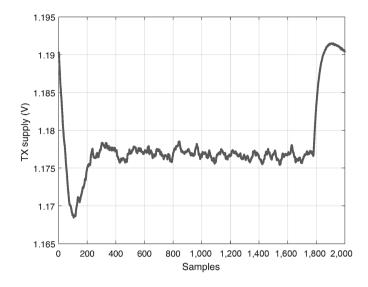

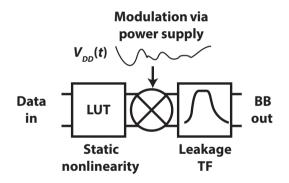

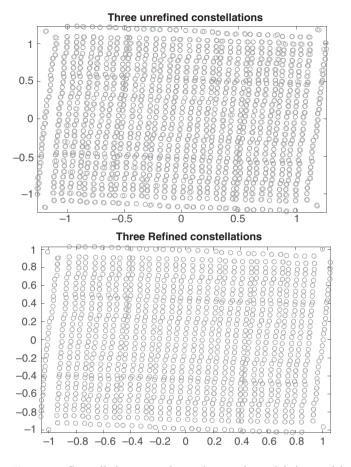

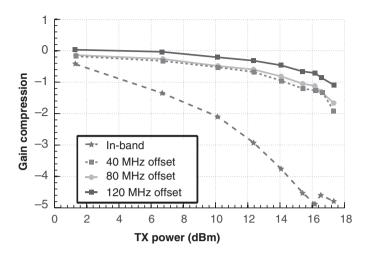

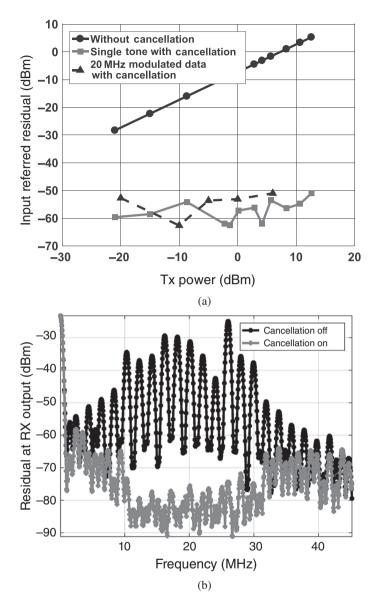

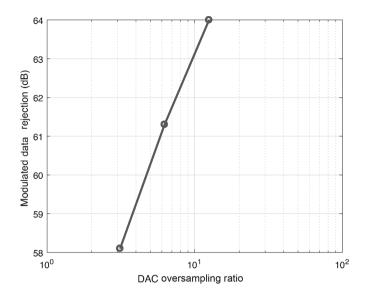

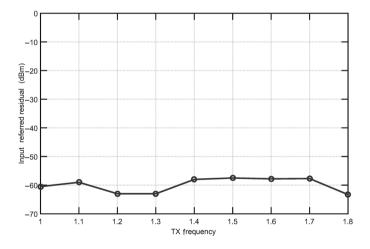

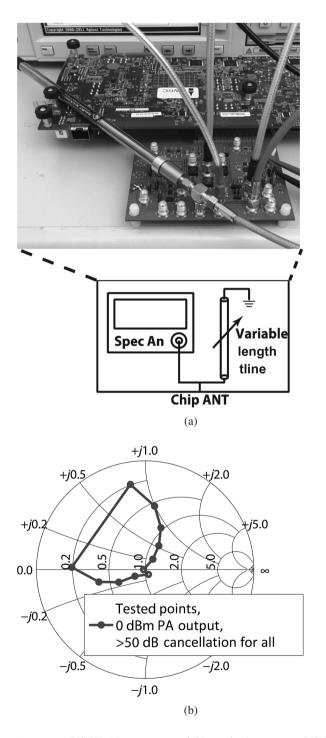

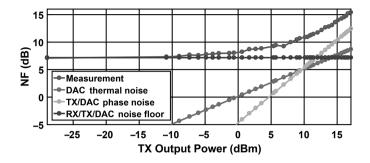

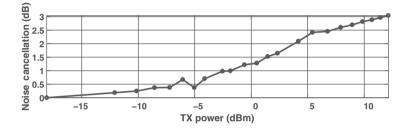

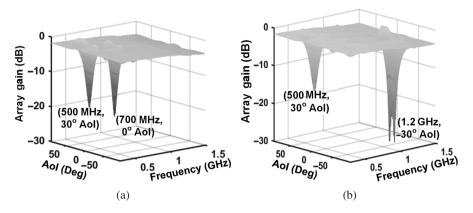

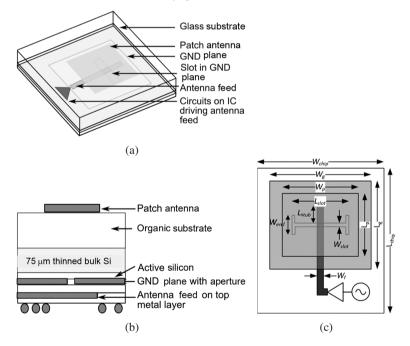

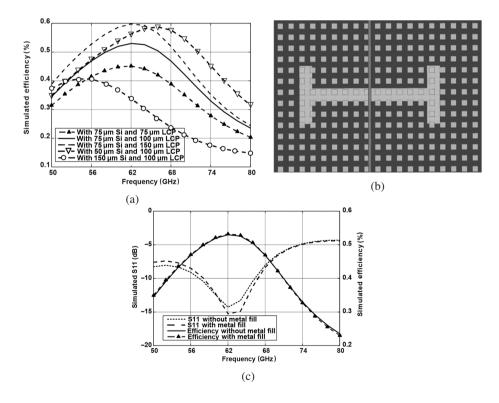

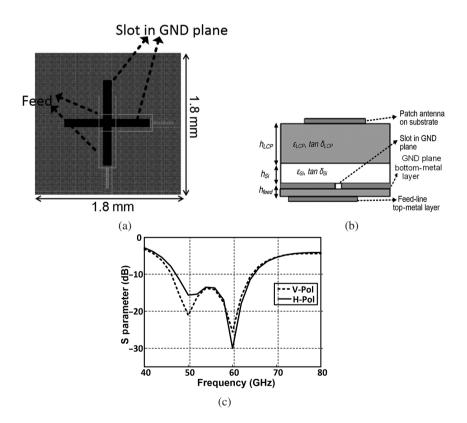

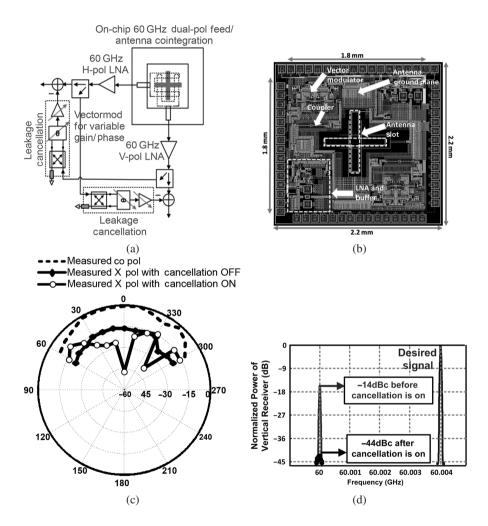

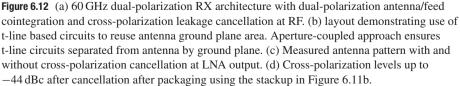

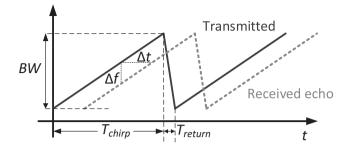

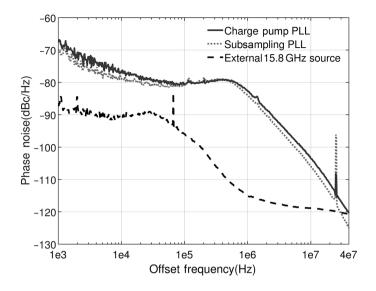

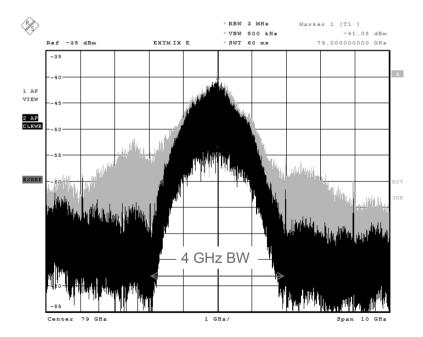

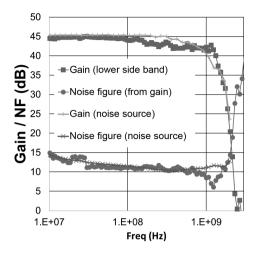

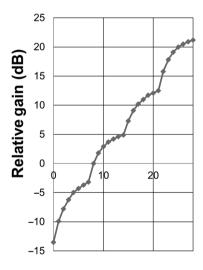

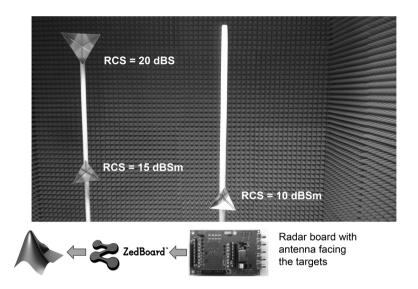

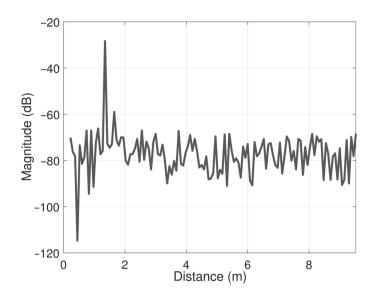

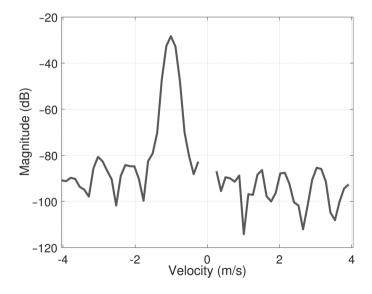

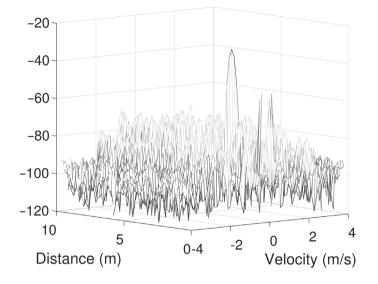

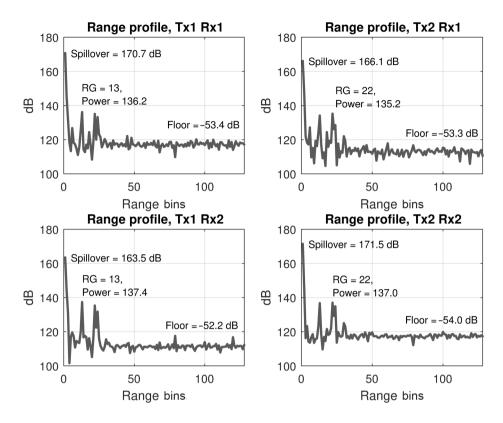

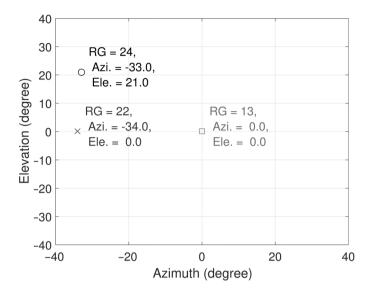

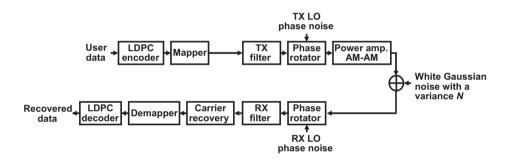

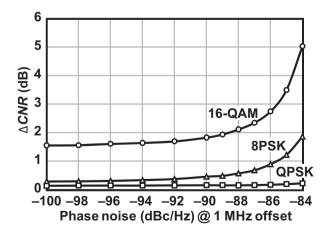

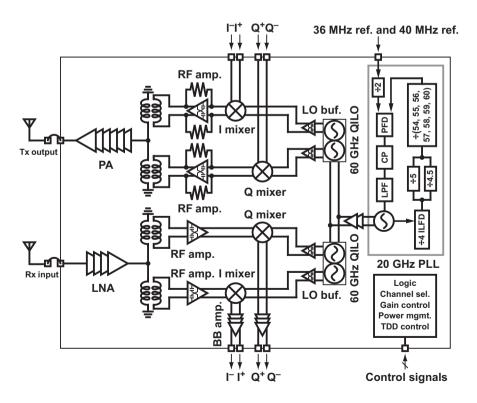

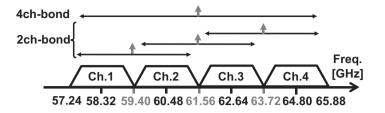

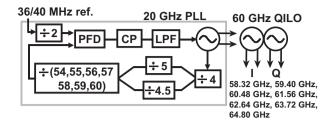

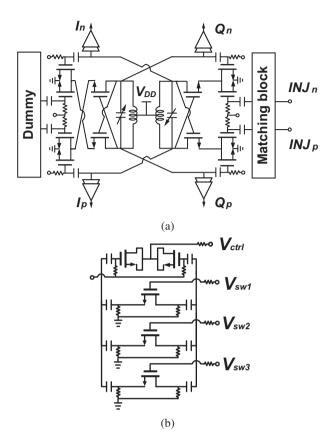

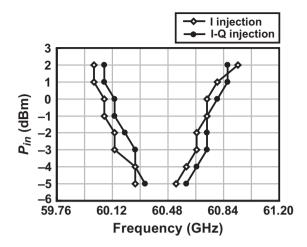

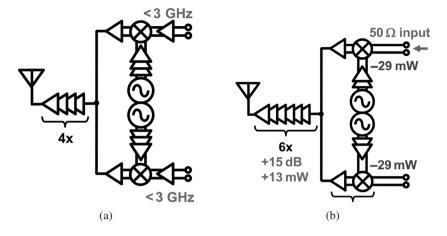

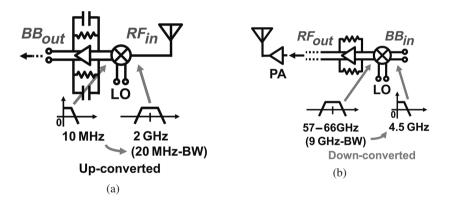

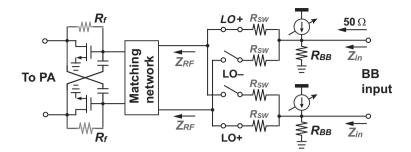

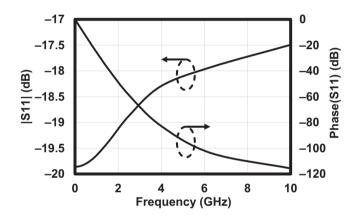

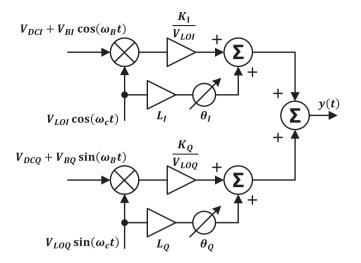

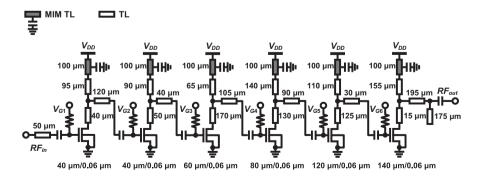

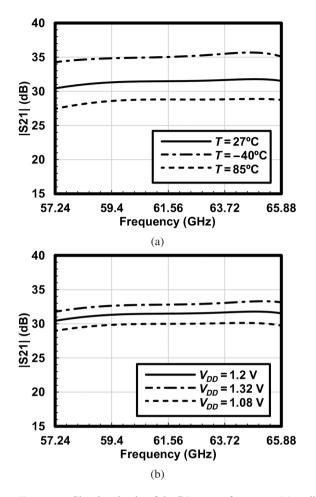

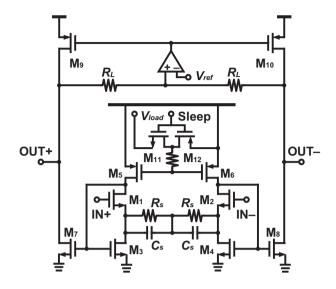

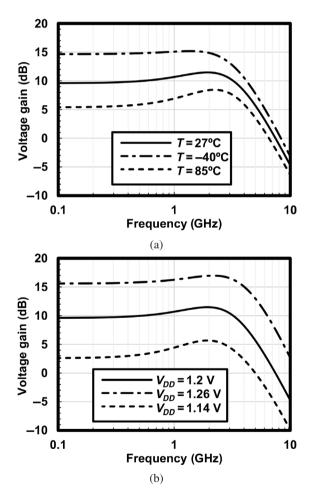

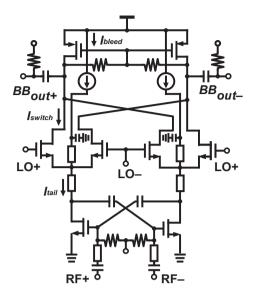

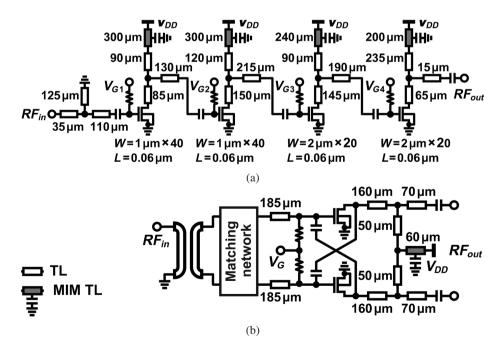

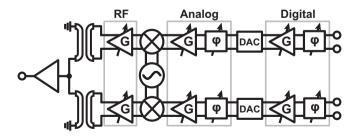

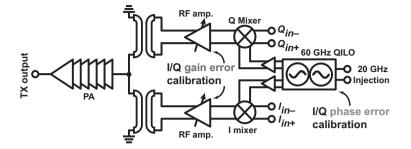

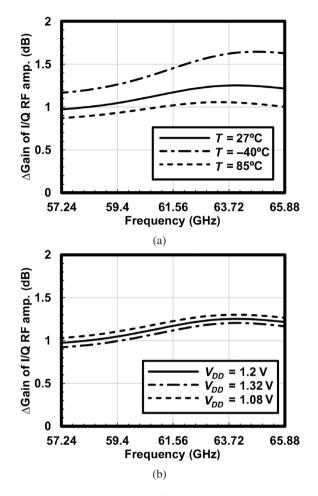

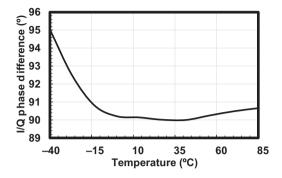

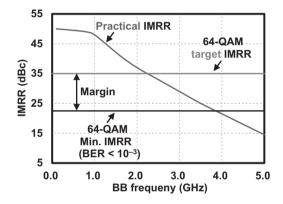

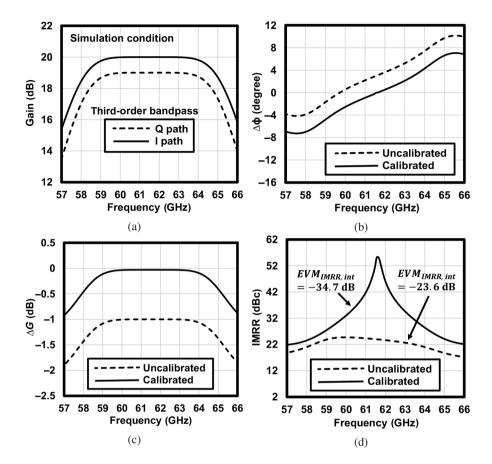

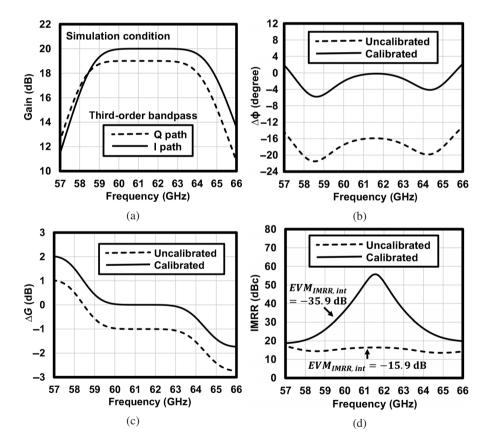

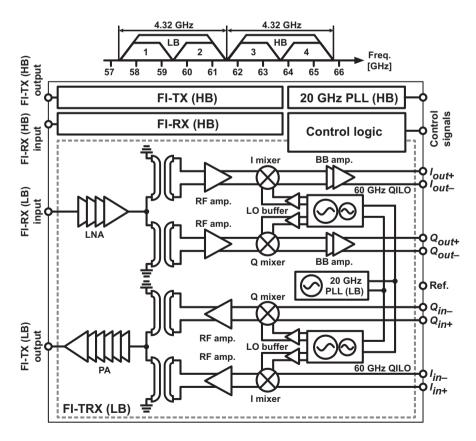

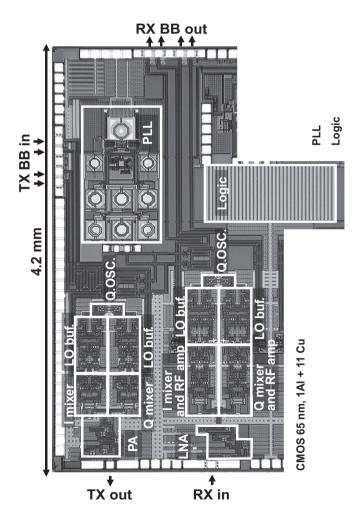

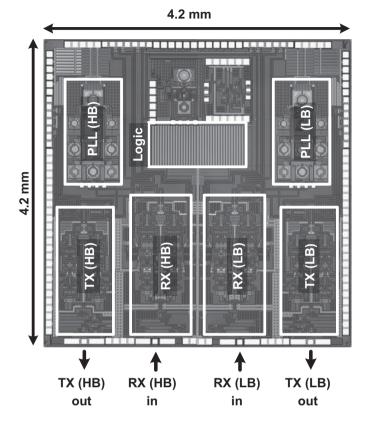

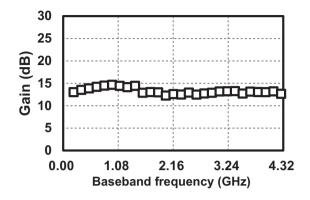

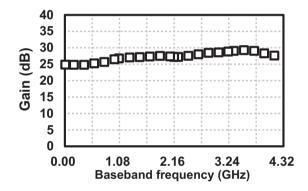

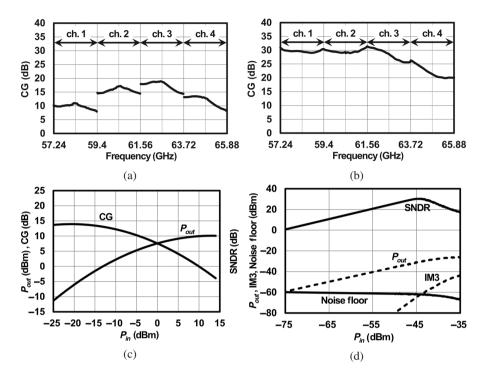

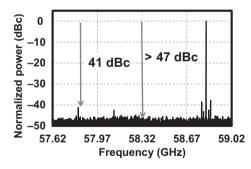

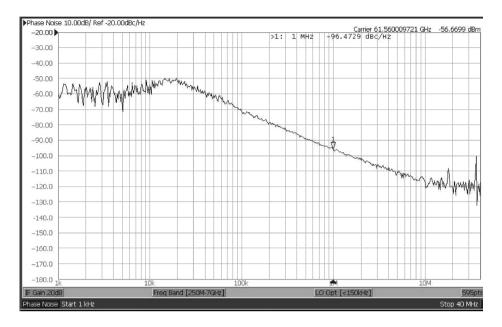

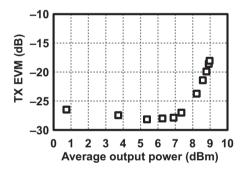

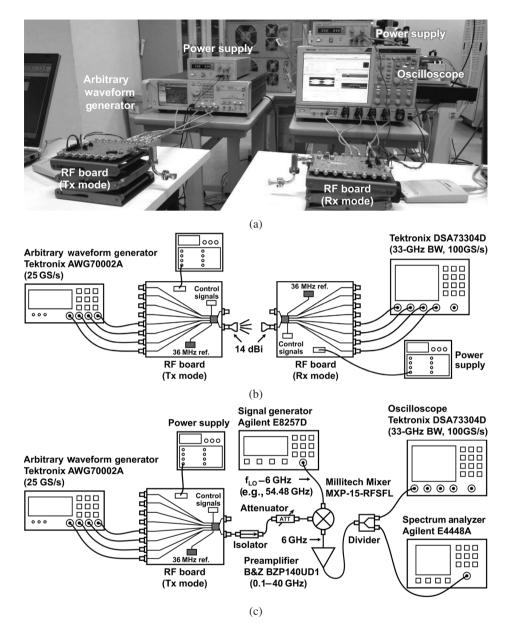

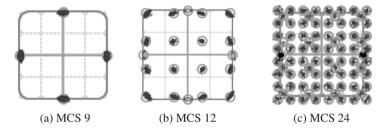

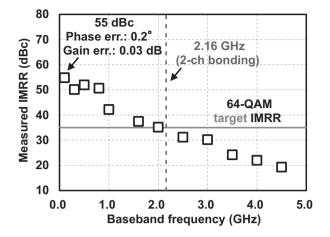

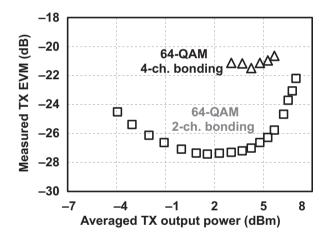

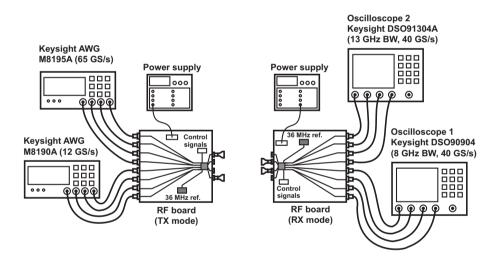

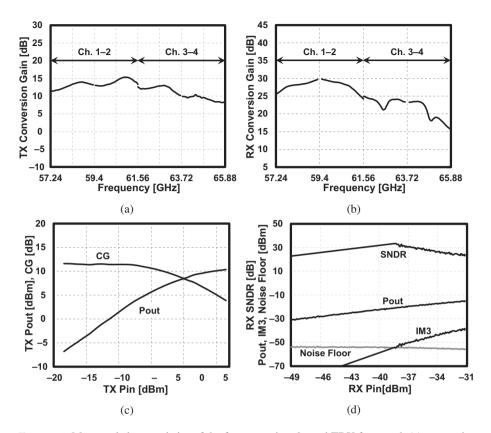

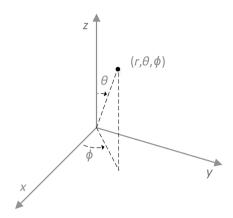

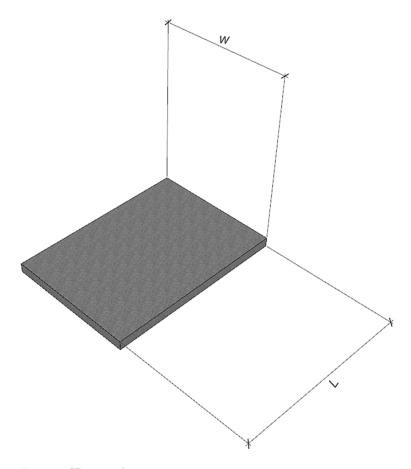

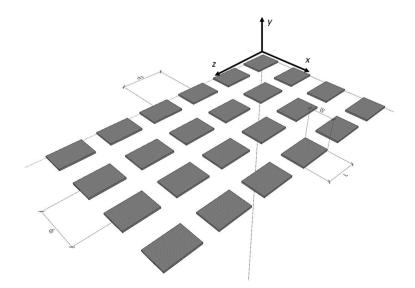

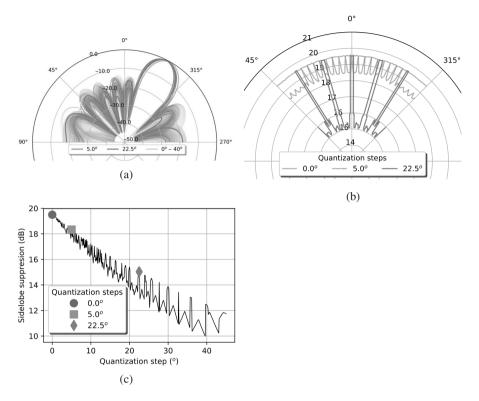

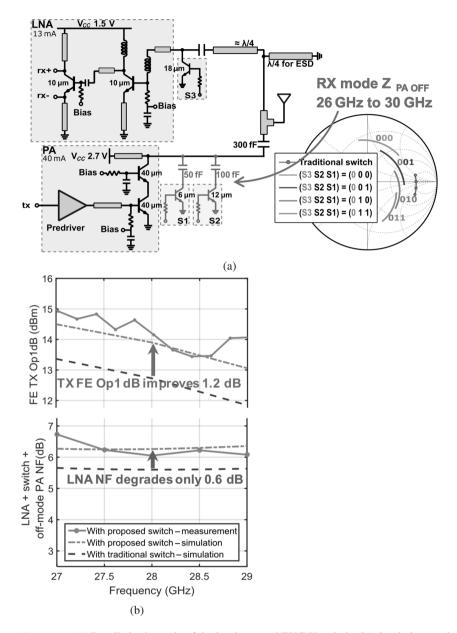

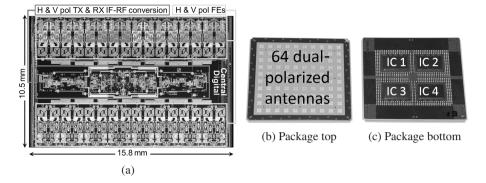

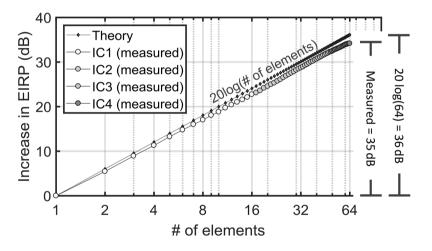

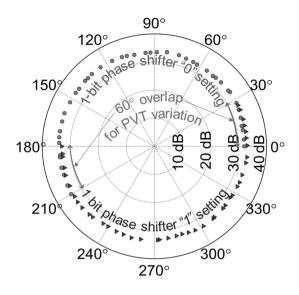

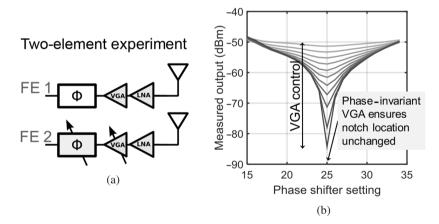

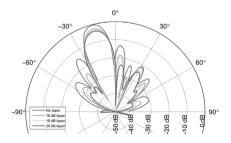

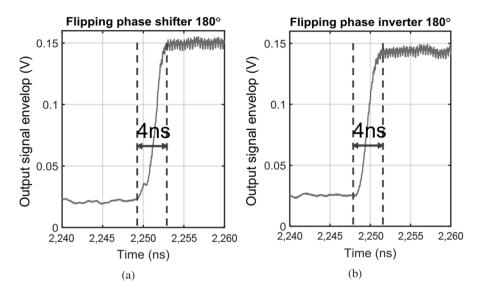

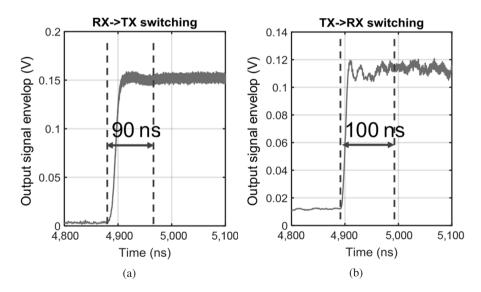

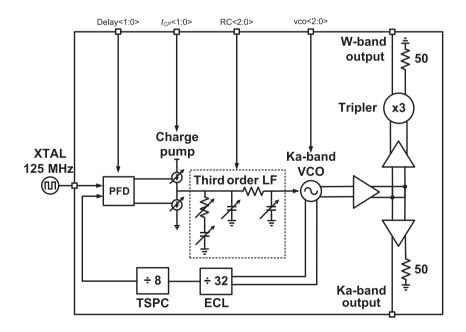

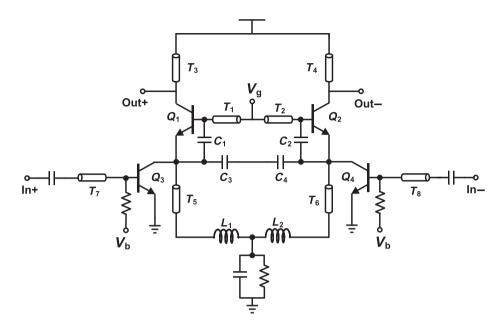

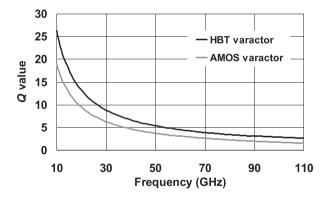

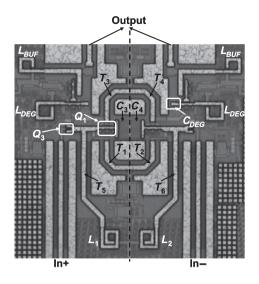

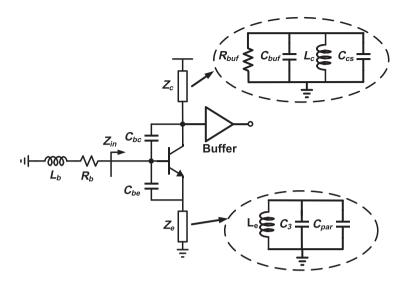

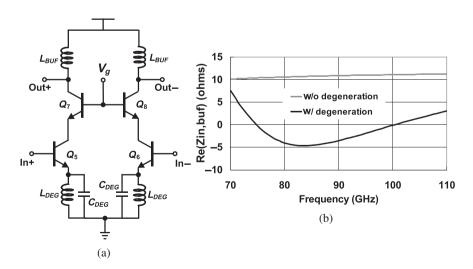

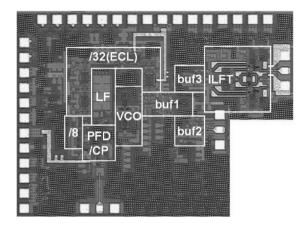

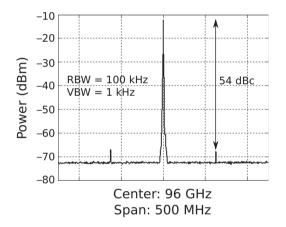

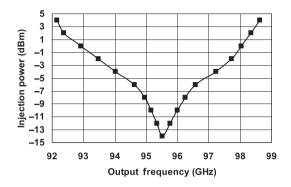

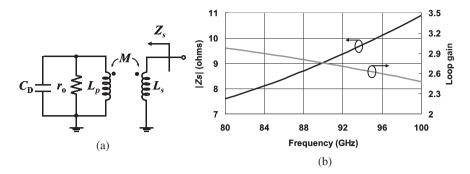

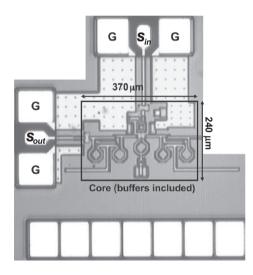

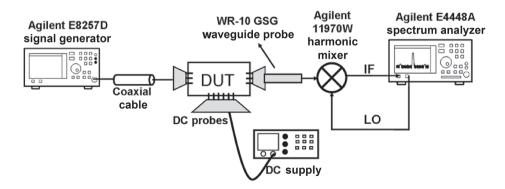

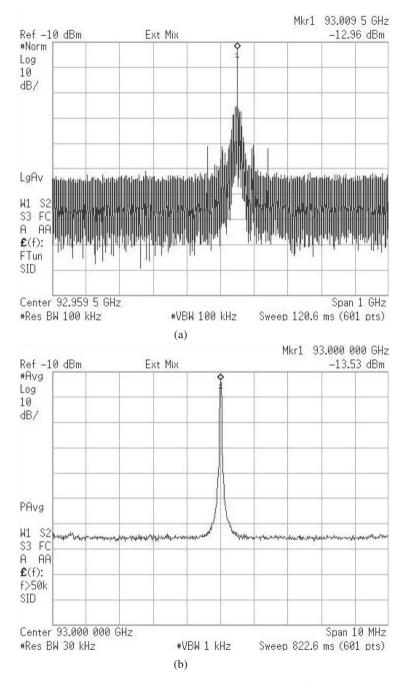

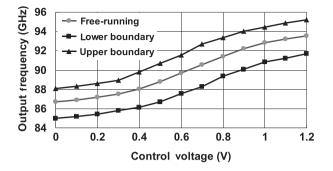

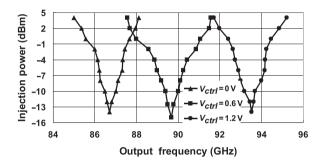

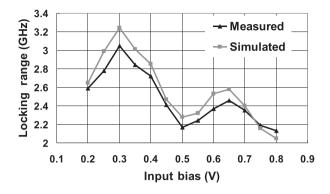

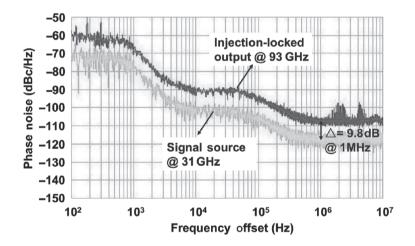

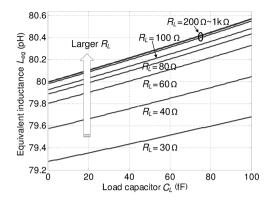

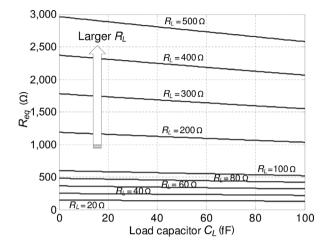

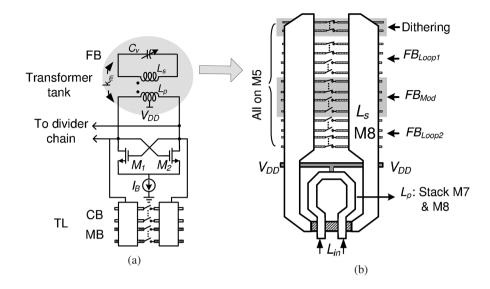

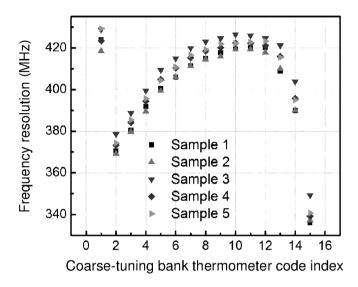

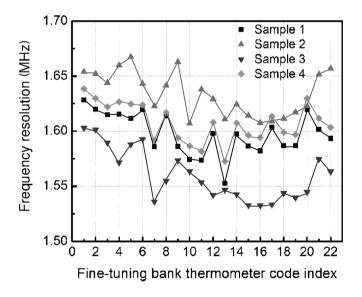

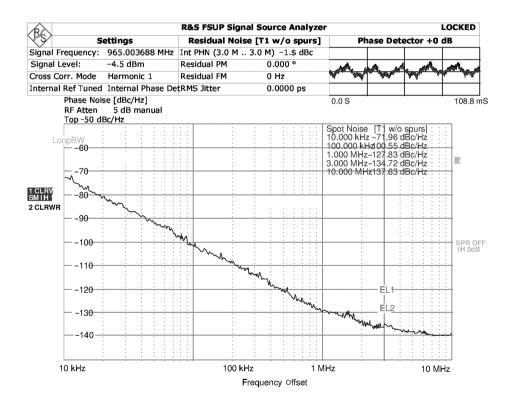

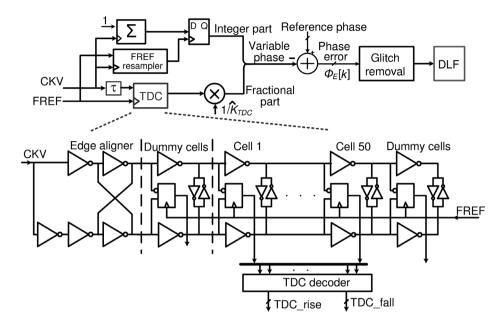

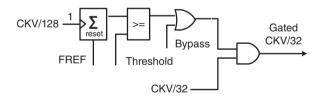

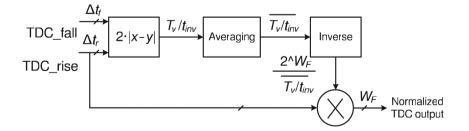

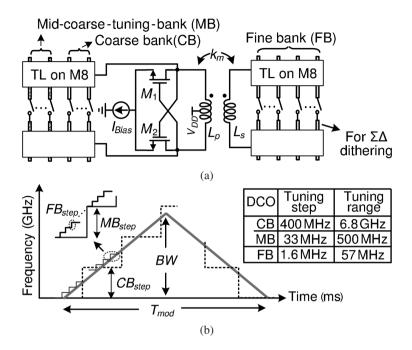

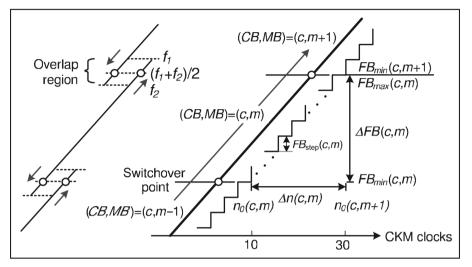

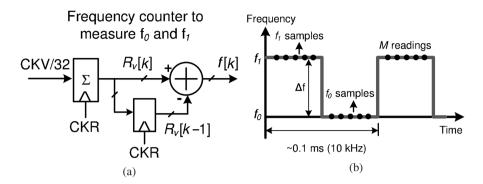

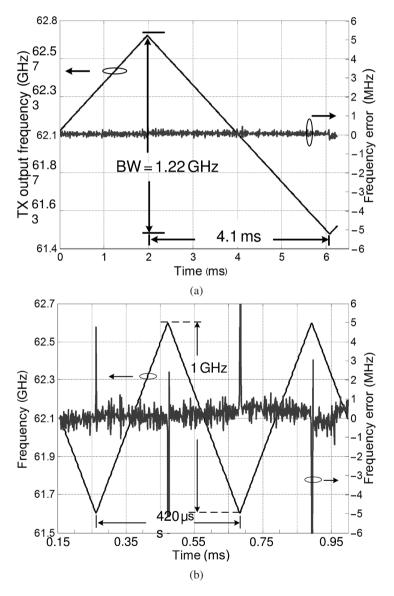

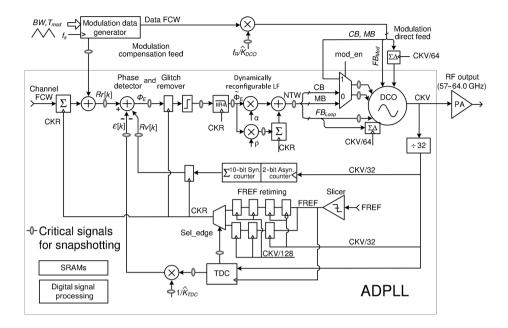

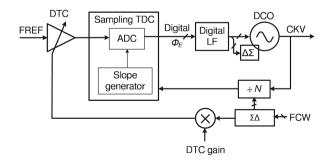

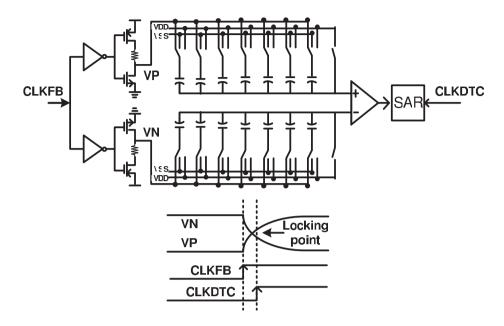

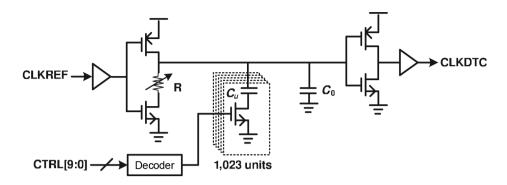

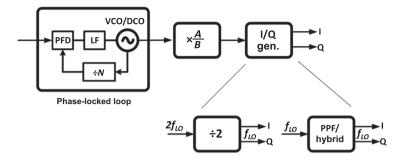

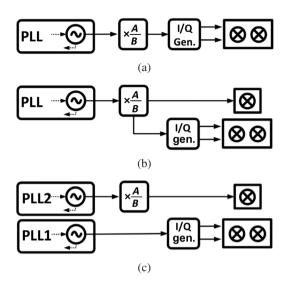

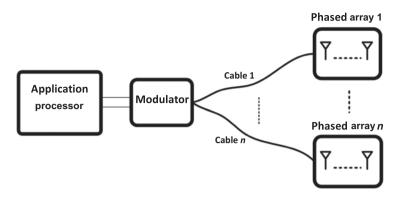

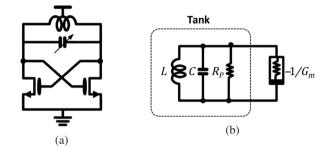

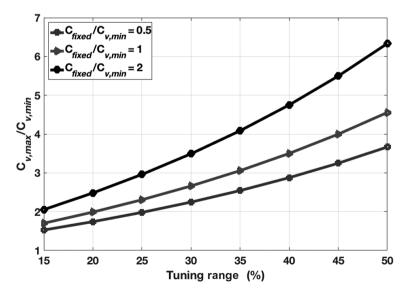

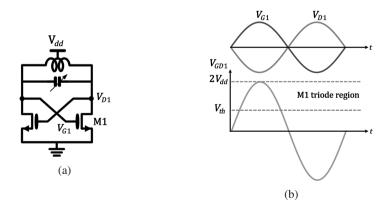

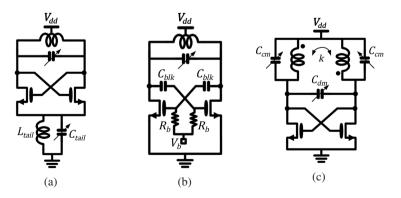

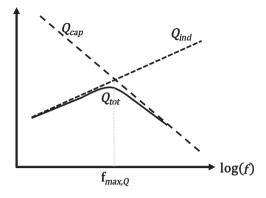

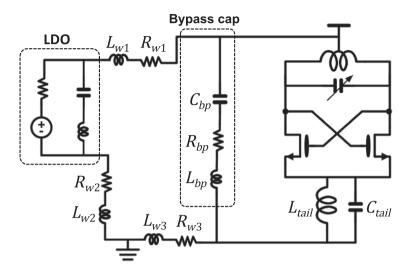

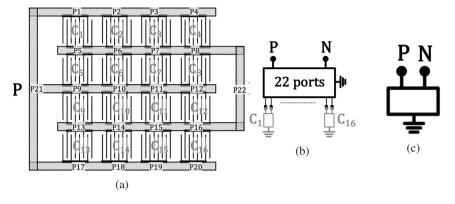

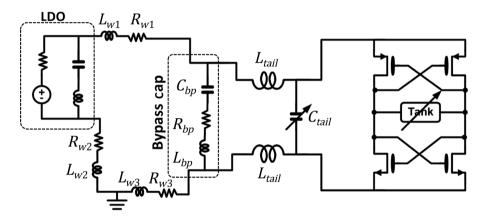

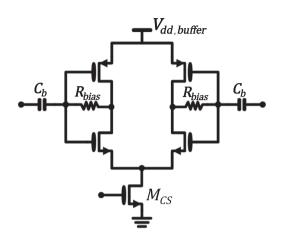

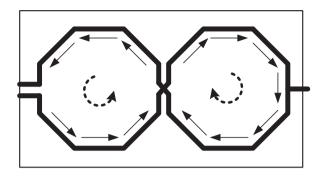

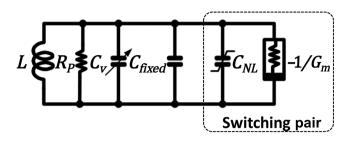

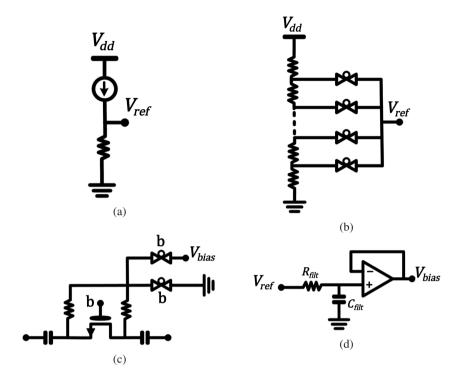

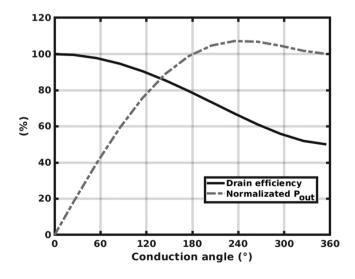

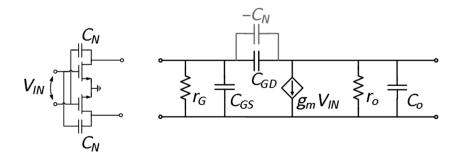

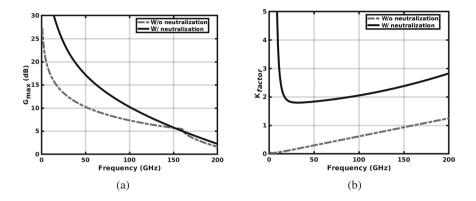

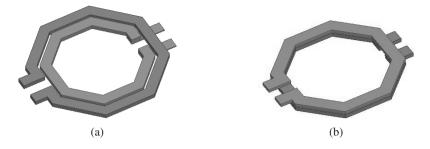

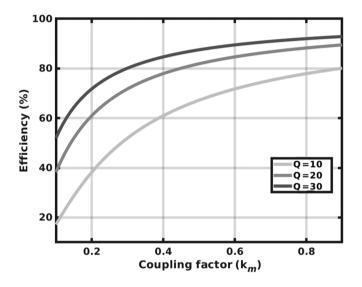

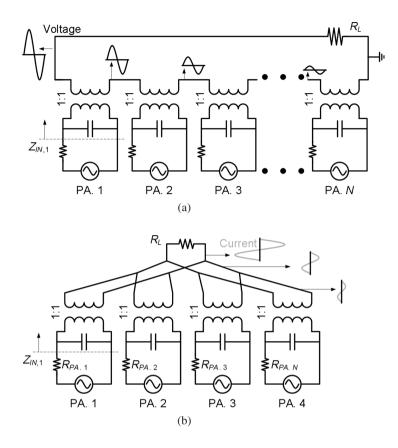

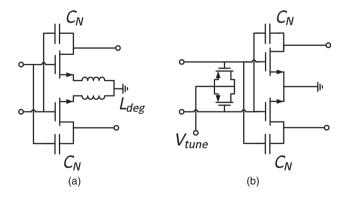

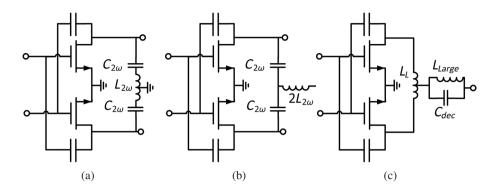

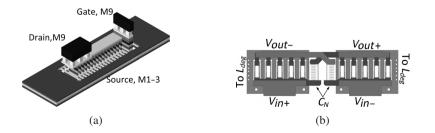

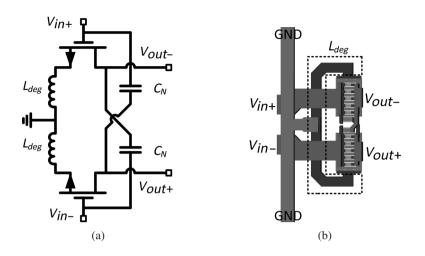

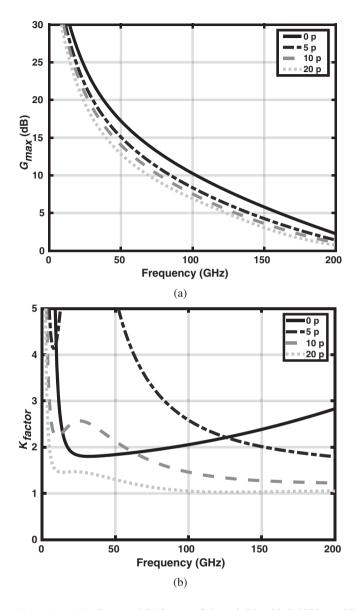

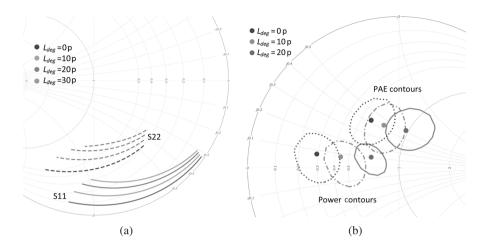

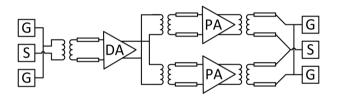

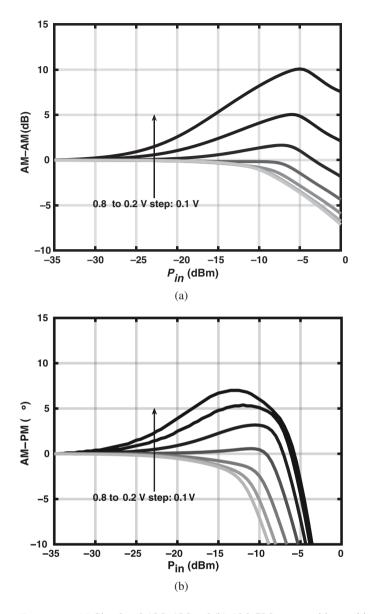

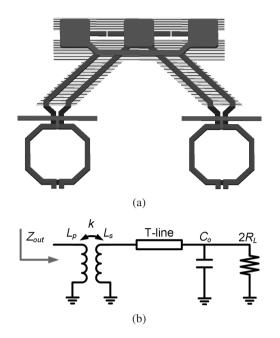

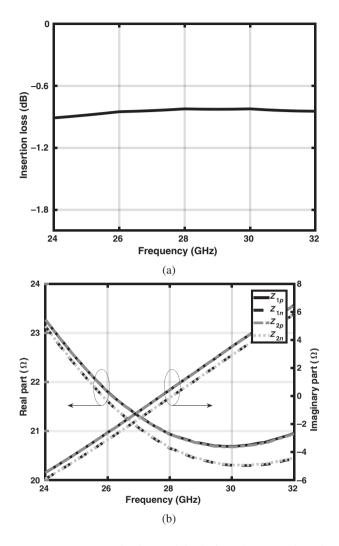

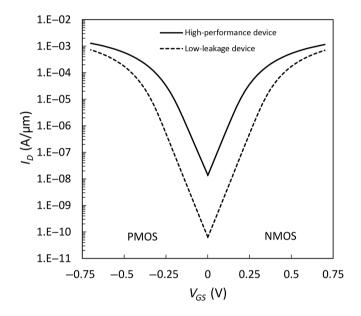

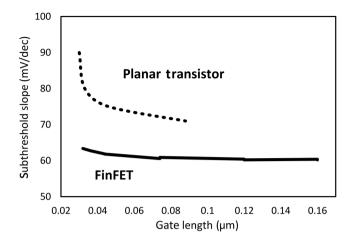

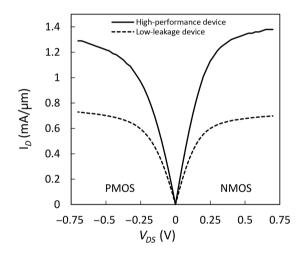

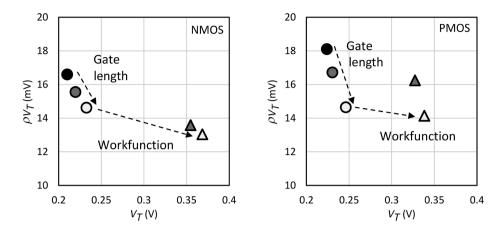

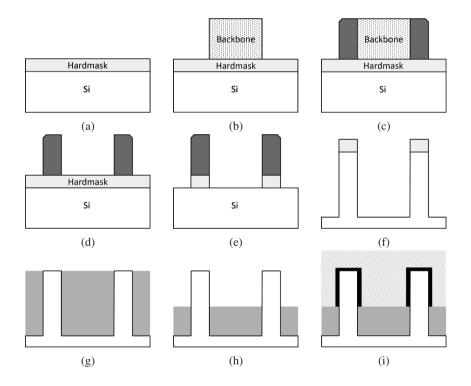

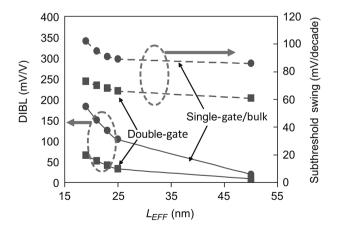

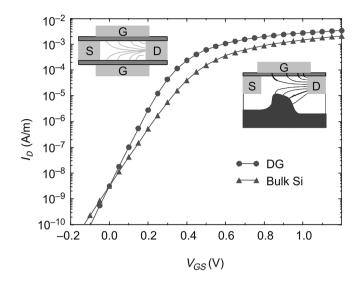

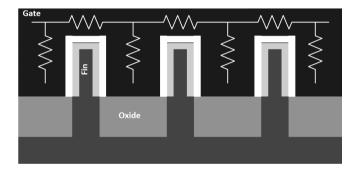

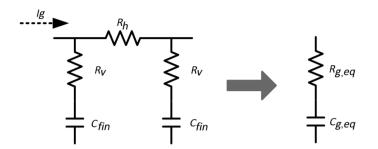

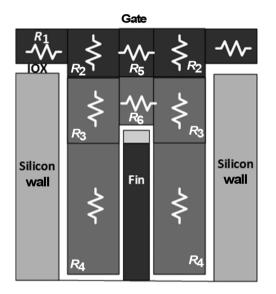

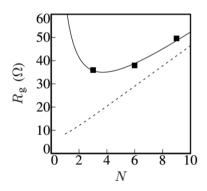

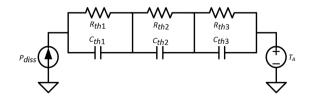

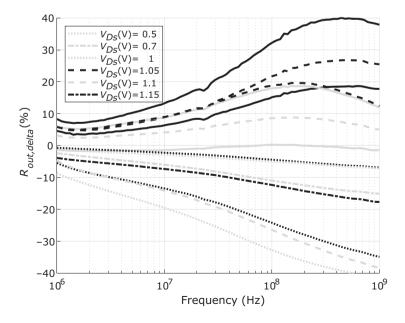

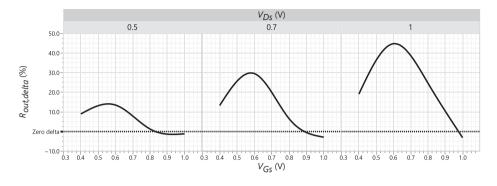

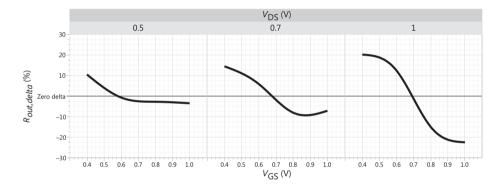

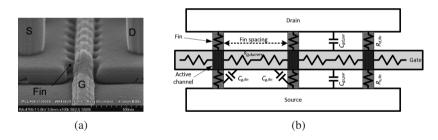

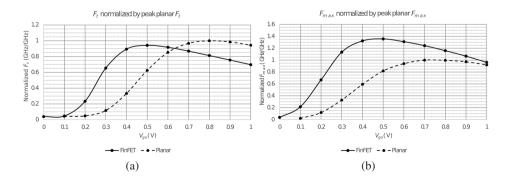

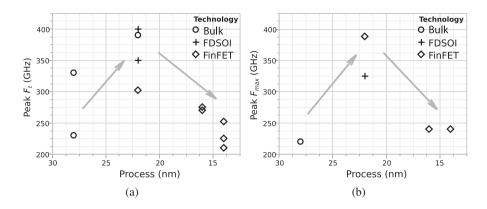

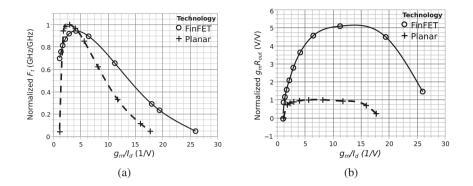

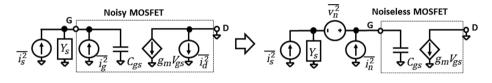

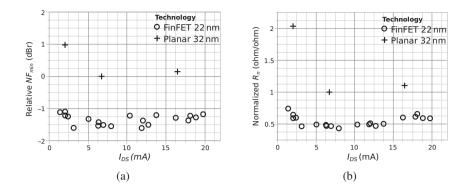

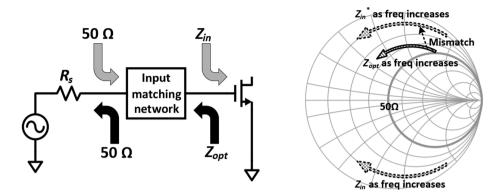

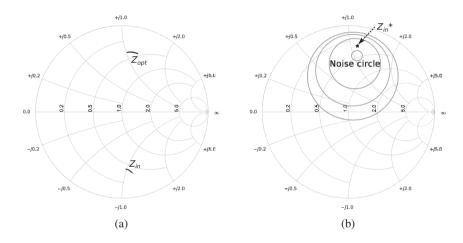

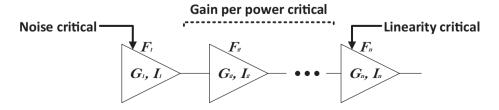

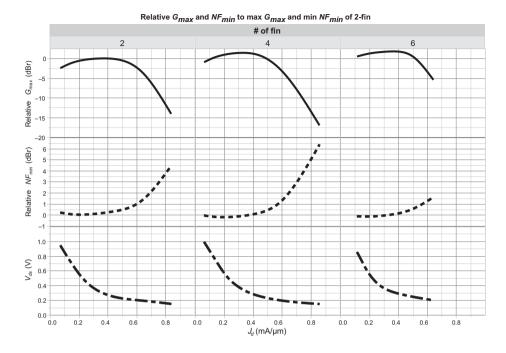

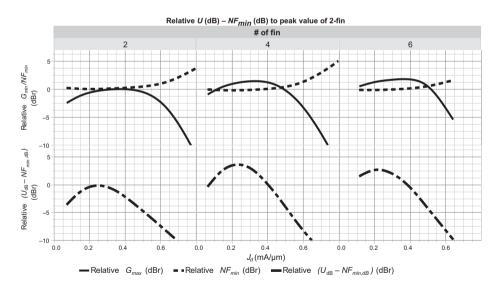

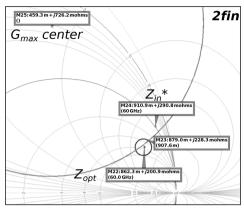

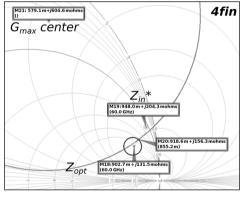

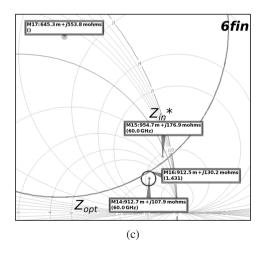

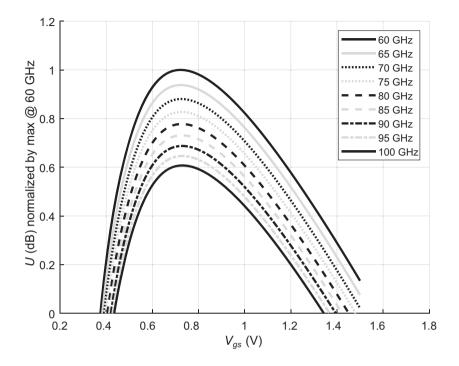

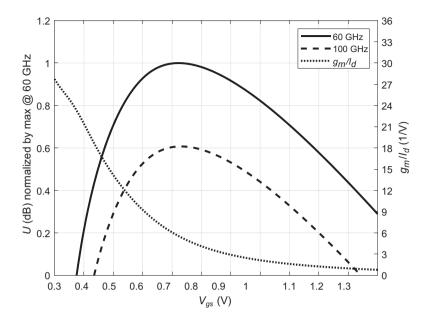

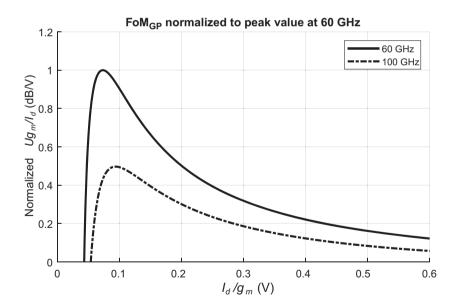

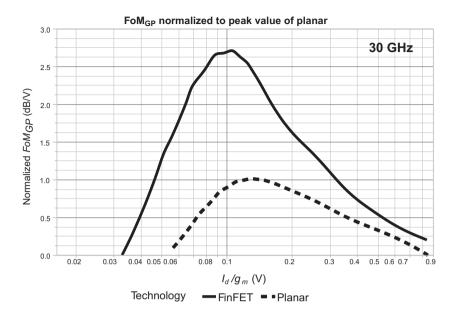

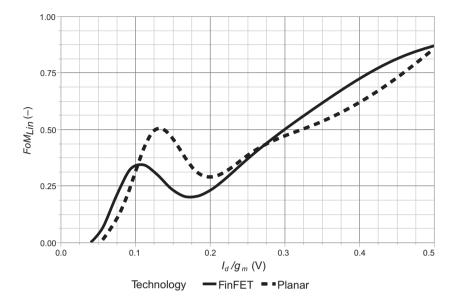

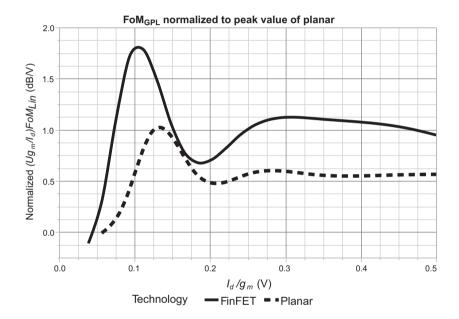

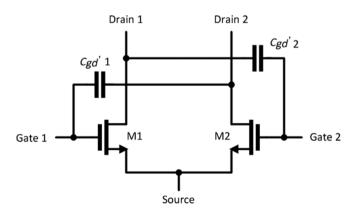

As alluded to earlier, mm-wave systems need beamforming to improve the SNR and to overcome the high path loss, but this is actually a great benefit of these systems, as they constrain energy to a beam rather than spreading the energy out over a wide area. This means more efficient transmitters and less interference, allowing higher spatial multiplexing and reuse of spectrum in adjacent sectors. Beamforming and MIMO technology are described in detail in Chapters 3, 6, and 9, with an emphasis on the circuit, package, and antenna side provided in Chapter 9.